TASKING, Andes, and MachineWare Team Up to Facilitate Rapid Development of RISC-V ASIL Compliant Automotive Silicon

- Post author:Peng Murphy

- Post published:2023-11-06

- Post category:Press Release

To support SoC design teams in the realm of firmware and MCAL development

Munich, Germany – Nov. 6, 2023 – TASKING’s system-level verification and debugging tools now support the Andes RISC-V ISO 26262 certified Processor IPs and associated MachineWare Virtual Models. This collaboration equips SoC design teams with automotive-grade RISC-V IPs and the appropriate tools for early firmware and MCAL (Microcontroller Abstraction Layer) development.

TASKING has been serving the global automotive industry for more than 30 years with software development tools certified for functional safety and cybersecurity. The toolset released as part of the collaboration provides the capabilities for multi-core, multi-hart, verification, debugging, performance tuning, timing, and coverage analysis. The toolset can be used with Andes RISC-V development boards and MachineWare high-performance virtual prototyping solutions. Moreover, the innovative TASKING iSYSTEM debug adapters will be available to support Andes RISC-V processors to enable the connection with the toolset.

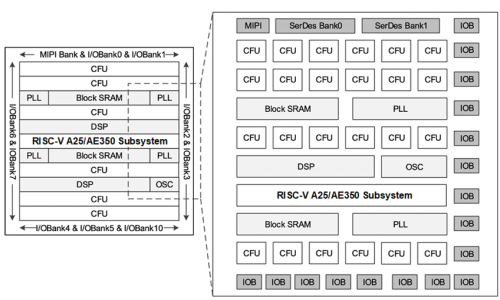

Andes Technology, a prominent provider of high-efficiency, low-power 32/64-bit RISC-V processor cores, introduced the first ISO 26262 fully compliant RISC-V processor IP – N25F-SE in 2022 with ASIL-B certification. Andes is also gearing up to unveil the ASIL-B certified D25F-SE equipped with RISC-V P-extension (SIMD/DSP) ISA draft for efficient manipulation of multiple data in a single instruction in the fourth quarter of 2023. Furthermore, Andes is working to deliver mission-critical ASIL-D certified cores based on their popular CPU IPs. The goal of this partnership is to offer comprehensive support for functional safety solution development, particularly in the realm of firmware and MCAL development. These resources will subsequently be employed by their customers within the automotive supply chain.

MachineWare’s ultra-fast virtual prototypes facilitate simulation of complex hardware/software systems for software analysis, verification and development as well as architecture exploration. With SIM-V MachineWare offers a high-speed RISC-V simulator that can be integrated in a full-system simulation, or Virtual Platform (VP) to simulate entire SoCs or ECUs. Besides pre-silicon availability, VPs offer many advantages over physical prototypes, as they enable for deep, non-intrusive introspection and are extremely scalable either on-premise or in the cloud.

The combination of products from the three companies enables users to switch seamlessly between virtual and physical SoCs, applying the same tools and automation scripts without any changes to the users’ process. This allows software developers to start the development process before silicon is available and identify and fix potential bugs and security issues at an early stage, shortening time-to-market.

Gerard Vink, responsible for RISC-V at TASKING, is excited about the collaboration of the three companies: “This partnership offers an integrated solution needed to drive the adoption of RISC-V based SoCs in the automotive domain. The certified IPs and tools reduce the efforts of all parties in the supply chain to comply with functional safety and cybersecurity requirements, enabling them to focus on innovation and product differentiation.”

“Andes’ ISO 26262 certified RISC-V IP offers solid, unprecedented flexibility and efficiency in silicon development,” said Samuel Chiang, Deputy Marketing Director of Andes, “Together with TASKING and MachineWare, we empower customers in the automotive industry to accelerate their development efforts, ensuring the successful achievement of functional safety and cybersecurity protection.”

“Our ultra-fast SIM-V functional RISC-V simulator empowers engineers to simulate complex hardware/software systems long before physical prototypes are even available. This speeds up the development process and reduces expensive bugs,” said Lukas Jünger, co-founder of MachineWare. “We are proud to collaborate with TASKING and Andes to offer our customers the tools they need for developing SoCs for the automotive industry.”

For more detailed information about the partnership and the three companies, please visit www.tasking.com, www.andestech.com and www.machineware.de.

About Andes Technology

Eighteen years in business and a Founding Premier member of RISC-V International, Andes is a publicly listed company (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099), a leading supplier of high-performance/ low-power 32/64-bit embedded processor IP solutions, and the driving force in taking RISC-V mainstream. Its V5 RISC-V CPU families range from tiny 32-bit cores to advanced 64-bit Out-of-Order processors with DSP, FPU, Vector, Linux, superscalar, and/or multi/many-core capabilities. By the end of 2022, the cumulative volume of Andes-Embedded™ SoCs has surpassed 12 billion. For more information, please visit https://www.andestech.com. Follow Andes on LinkedIn, Twitter, Bilibili and YouTube!

About MachineWare

Established in 2022 in Aachen, Germany, MachineWare is a pioneering company specializing in the creation of high-performance simulators for entire electronic systems, commonly referred to as Virtual Platforms (VPs). These cutting-edge VPs are designed to execute unmodified target software, serving as indispensable tools for development, verification, and architecture exploration.

One of MachineWare’s flagship offerings, SIM-V, stands out as a versatile and rapid solution tailored for virtualizing RISC-V systems. SIM-V empowers users to accelerate their RISC-V software development process, allowing them to meet and exceed their schedules by helping to identify software defects, such as bugs and vulnerabilities long before physical prototypes are available.

MachineWare’s products and services simplify hardware/software integration by providing a unified toolset for both hardware and software designers early in the system design cycle. This approach facilitates a smoother development process and superior end products. Visit https://www.machineware.de for more details.

About TASKING

TASKING is a leading provider of development tools headquartered in Munich, Germany, offering high-performance, high quality, safety & security-oriented embedded software development tools for multi-core architectures.

TASKING’s development tools are used by automotive manufacturers and suppliers, as well as in adjacent markets around the world to realize high-performance applications in safety-critical areas.

The TASKING Embedded Software Development solutions provide an industry-leading ecosystem for your entire software development process. Each TASKING compiler is designed for a certain architecture and meets the specific requirements of your industry, including automotive, industrial, telecommunications and datacom.

As the recognized leader in high-quality, feature- and safety-compliant embedded software development tools, TASKING enables you to create code with best-in-class size and performance with compilers, debuggers and RTOS support for industry-leading microprocessors and microcontrollers.

Since February 2021, TASKING has been majority-owned by financial investor FSN Capital, which has put the group on a long-term growth path following a successful carve-out. For more information visit www.tasking.com or follow us on https://www.linkedin.com/company/tasking-inc.