Home | Product & Solutions | AndesCore™ Processors | RISC-V:NX27V

AndesCore™ NX27V Processor

64-bit CPU with RISC-V Vector Extension

AndesCore™ NX27V Overview

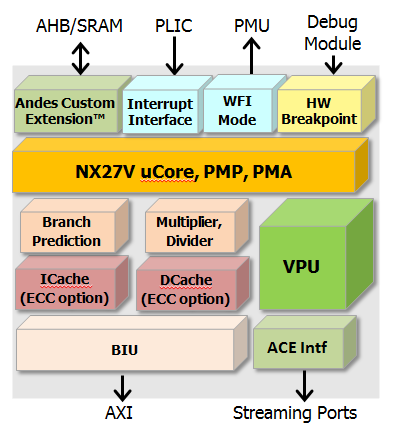

- AndeStar™ V5 Instruction Set Architecture (ISA), compliant to RISC-V technology

- RISC-V vector extension

- Vector Processing Unit (VPU) boost the performance of AI, AR/VR, computer vision, cryptography, and multimedia processing

- Andes extensions, architected for performance and functionality enhancements

- Separately licensable Andes Custom Extension™ (ACE) for customized acceleration

- 64-bit CPU architecture, enabling software to utilize the memory spaces far beyond 4G bytes imposed by 32-bit CPUs

- 16/32-bit mixable instruction format for compacting code density

- Branch predication to speed up control code

- Return Address Stack (RAS) to speed up procedure returns

- Physical Memory Protection (PMP) and Programmable Physical Memory Attributes (PMA)

- MemBoost for heavy memory transactions

- Flexibly configurable Platform-Level Interrupt Controller (PLIC) for supporting wide range of system event scenarios

- Enhancement of vectored interrupt handling for real-time performance

- Advanced CoDense™ technology to further reduce code size on top of “C” extension

The 64-bit NX27V is a vector processor with 5-stage scalar pipeline that supports the latest RISC-V specification, including the IMAFD standard instructions, “C” 16-bit compression instructions, “P” DSP extension instructions, “V” vector extension instructions and “N” for user-level interrupts. It brings enhanced performance in memory subsystem with higher memory bandwidth and memory latency reduction by supporting multiple outstanding data access. NX27V features branch prediction, instruction and data caches, local memories, ECC error protection, and Andes Custom Extension™ (ACE) to add proprietary instructions to accelerate performance/power consumption critical spots. It also includes vectored and preemptive interrupts to serve diversified system events. AXI data bus for wide data access, PowerBrake and WFI mode for rich power management, and JTAG debug interface and trace interface for software development support. NX27V contains powerful Vector Processing Unit (VPU). It is ideal for applications with large arrays of data such as machine/deep learning, AR/VR, cryptography, multimedia processing, networking and scientific computing.

Development Tools

- AndeSight™ Integrated Development Environment

- COPILOT: Custom-OPtimized Instruction deveLOpment Tool for ACE

- ICE debugging hardware

Key Features and Performance

AndeStar™ V5 Architecture

| Key Features | Benefits |

|---|---|

| RISC-V RV64GC-N-P-V ISA |

|

| 64-bit CPU architecture | Enabling software to utilize the memory spaces far beyond the 4G byte limit of 32-bit CPUs |

| RISC-V V-extension instructions with versatile operations | Boost the performance of AI, AR/VR, computer vision, cryptography, and multimedia processing |

| Andes Extended Instructions | Andes exclusive performance and functionality enhancements |

| Andes Custom Extension™ (ACE) option to create customized instructions for software acceleration |

|

| 16/32-bit mixable instruction format | For compact code density |

| 32 general-purpose registers | For better code size and performance |

| Machine (M),User (U) | Embedded systems with privilege protections |

CPU Core

| Key Features | Benefits |

|---|---|

| 3.52 Coremark/MHz, 2.09 DMIPS/MHz* | Superior performance-per-MHz |

| 5-stage pipeline, with a full-cycle reserved for critical SRAM accesses | Superior performance-efficiency, while allowing for high speeds |

Extensive branch predication features

|

|

Vector Processing Unit (VPU)

|

|

| Physical Memory Protection (PMP), 16 regions | Basic read/write/execute memory protection with minimum cost |

| Programmable Physical Memory Attribute (PMA), 16 regions | Configurable memory attributes:

|

| Performance monitors | Program code performance tuning |

| StackSafe™ hardware stack protection |

|

Multiplier options

| Option to choose between speed and area according to application's requirements |

| PowerBrake technology | Performance throttling to digitally reduce power consumption |

| QuickNap™ technology | Fast power-down/wake-up support for caches |

* BSP v5.0.0, DMIPS/MHZ follow Dhrystone’s no-inline ground rules, best performances

Memory Subsystems

| Key Features | Benefits |

|---|---|

I-Cache & D-Cache

|

|

| MemBoost – Data Cache Write-Around | Smart cache line allocation policy, for better cache utilization and reduce number of memory accesses |

| MemBoost – Instruction and Data Pre-fetch | Conditionally fill instruction and data caches in advance, for minimum memory access latency |

| MemBoost – Multiple Outstanding Mem. Req. | Issue multiple transactions to data memory sub-system for higher bus utilization, also support out-of-order completion |

| MemBoost – Dedicated I & D Bus Interfaces | Separate instruction and data buses, for instruction and data’s own memory transactions |

| Soft-error protection: ECC or parity for I-Cache and D-Cache | Code and data integrity protection |

| Bus master port: AXI bus with data width matching configurable memory width | User-selectable configuration for optimal efficiency |

Platform-Level Interrupt Controller (PLIC)

| Key Features | Benefits |

|---|---|

Implements RISC-V PLIC specification

| Allow individual interrupts to be serviced and prioritized without sharing |

Enhanced interrupt features

|

|

Debug Support

| Key Features | Benefits |

|---|---|

| Implements RISC-V debug specifications | Supported by industry debug tool suppliers |

| JTAG Debug Port | Industry-standard support |

| Embedded Debug Module with up to 8 triggers | Flexible configurations to tradeoff between gate count and debugging capabilities |

| Exception redirection support | Entering debugger upon selected exceptions without using breakpoints |

Product Package

AndesCore™ NX27V Processor with AE350 Platform

- Pre-integrated NX27V with CPU subsystem (including PLIC, Timer and Debug Module), and AXI platform