Andes Technology Issues GDR to Be Listed on Luxembourg Stock Exchange for Expansion Plan

- Post author:Rachel Miaou

- Post published:2021-10-29

- Post category:Press Release

San Jose, California – October 29, 2021 – Andes Technology (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099), a leading RISC-V CPU IP supplier, announced today that it successfully issued its overseas depositary receipts (GDR) on the Luxembourg Stock Exchange on September 13. Each newly issued overseas depositary receipts unit will represent 2 ordinary shares, and its initial market value is priced at US$31.78, which is approximately NT$440 per share. A total of 4 million units are issued, representing 8 million shares of common stock. The total amount raised overseas is approximately US$127 million (NT$3.517 billion). Andes Technology is currently the only public RISC-V CPU IP supplier, and the GDR shareholders are mainly foreign institutional investors who aim for long-term investment.

“The funding allows Andes to achieve the main goal of boosting medium-term and long-term capital investing in R&D and expanding product lines, especially high-end products, “Frankwell Lin, Chairman and CEO of Andes Technology stated. “Moreover, global investors are able to share the fast-growing RISC-V market. To meet the urgent demand for RISC-V high-end computing solutions, the funds will be mainly put into accelerating the expansion of product design centers to strengthen our existing leading RISC-V product portfolio as well as speed up the development of high value and high-end RISC-V CPU IPs and SoC software and hardware integrated solutions. In order to seize the market of profitable high-end multicore CPU IPs and boost sales momentum, Andes’ design centers in Taiwan, United States and Canada plan to recruit 200 R&D talents to develop the next-generation RISC-V products for applications including 5G, artificial intelligence/machine learning, HPC, ADAS, automotive electronics, AR /VR, blockchain, cloud computing, data center, server, Internet of Things, MCU, storage devices, security, wireless devices, and other massive and high-performance computing markets.”

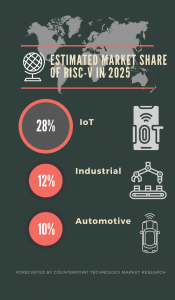

Andes reports revenue growth of 72.6% (YoY) in the first half of 2021 and 63% of the revenue is contributed by RISC-V products, including standard IP licensing and customization computing business. In addition, the revenue of 2020 is nearly doubled from that of 2018 when Andes started delivering its initial RISC-V cores. According to Counterpoint Research’s latest report, as semiconductor solutions require more and more versatile IPs, pure play semiconductor IP market size will grow at 11% CAGR to $8.6 billion per year by 2025. RISC-V is growing rapidly, due to its open-source advantage, easier power consumption optimization, reliable security functions and lower political risk impact. RISC-V processors will continue to see fast adoption across multiple categories including IoT, industrial and automotive, which are the key sectors with 28%, 12% and 10% adoption respectively by 2025. These favorable factors for market expansion will benefit Andes and its customers.

“Andes provides hardware IP, but just like software companies, our R&D manpower is a knowledge-intensive production line,” Dr. Charlie Su, President and CTO of Andes Technology said. “Since established, Andes has devoted tremendous resources into R&D and focused on developing the best processor IPs to shorten customer’s time-to-market. That is the main reason why Andes has been able to report record-breaking revenue throughout the years. To keep the growth momentum going, Andes will recruit more R&D talents around the world. Based on the solid foundation, we will extend our portfolio to cover more high-value products and address the demand for high-performance computing solutions and grow along with the booming market.”

Looking ahead to the coming decade, as more and more international technology companies are embracing RISC-V and expanding their market and applications, Andes is determined to continue to drive the RISC-V momentum as the leading pure play processor IP vendor. By leveraging years of extensive experience helping customers achieve mass production of diversified products, Andes will support even more RISC-V SoC design teams to introduce new products and its revenue and profit will advance with the soaring RISC-V market.

About Andes Technology

Sixteen years in business and a Founding Premier member of RISC-V International, Andes is a leading supplier of high-performance/low-power 32/64-bit embedded processor IP solutions, and a main force to take RISC-V mainstream. Andes’ fifth-generation AndeStar™ architecture adopted the RISC-V as the base. Its V5 RISC-V CPU families range from tiny 32-bit cores to advanced 64-bit cores with DSP, FPU, Vector, Linux, superscalar, and/or multicore capabilities. The annual volume of Andes-Embedded SoCs has exceeded 2 billion since 2020 and continues to rise. To the end of 2020, the cumulative volume of Andes-Embedded™ SoCs has reached 7 billion. For more information, please visit https://www.andestech.com. Follow Andes on LinkedIn, Twitter, Facebook, and YouTube!