Andes Presents Ground-Breaking 27-Series Processor at RISC-V Summit 2019

- Post author:Sheila

- Post published:2019-12-04

- Post category:Press Release

Configurable Vector Processor Enables Scalable Performance Beyond Any IP Core to Date Supported by High-Performance Memory Subsystems

Hsinchu, Taiwan and San Jose, California, December 4th, 2019 – Andes announces AndesCore™ 27-series CPU cores today and will present it at the RISC-V Summit. The 27-series is the first licensable RISC-V core to deliver to a production licensee the RISC-V Vector instruction extension (RVV), and to sustain the memory bandwidth and efficiency Andes has also re-architected its memory subsystem. Initial delivery of the CPU core has completed to Andes earliest licensee, with production release slated for Q1, 2020. Dr. Charlie Su, Andes Technology CTO and EVP will unveil details of this ground-breaking product at the Summit.

The advent of AI, AR/VR, computer vision, cryptography, and multimedia processing all require complex computation of large volume of matrix data. Unlike other vendor’s advanced SIMD, which has a narrow range of performance dictated by their architecture control, the RVV specification envisions a powerful instruction set with scalable data sizes, flexible microarchitecture implementations, and leaves memory subsystem decisions open for system level optimization. With the 27-series CPU cores, Andes delivers this unprecedented performance and flexibility to the RISC-V community and for the first time, enables RISC-V cores to fill the void in applications even other vendors have not been able to reach.

“The 27-series marks yet another important milestone in both Andes and RISC-V journey, and I couldn’t be more proud of our R&D team for this achievement,” said Andes President, Frankwell Lin. “The RVV extension boldly takes RISC-V beyond any licensable processor core technology into the hottest markets today, and our licensee’s confidence in the R&D team enables Andes to be the first to deliver on this ambitious vision. The team has worked together from specification to delivery in less than nine months. It’s one of the most thrilling journey in Andes history.”

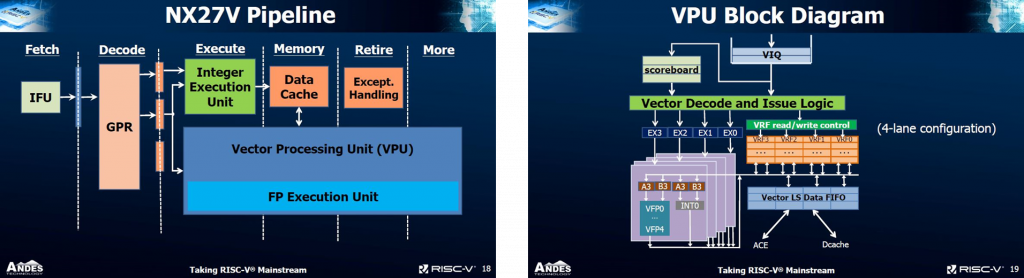

Initially available in the 27-series will be the 32-bit A27, and 64-bit AX27 and NX27V. They benefit from Andes proven 25-series cores, supporting the latest RISC-V specifications, subsystem level components, as well as ecosystem enablement from Andes’ 14-years of R&D development. The A27 and AX27, tailored for applications running Linux, offer 50% higher memory bandwidth than its 25-series predecessors. The NX27V contains a Vector Processing Unit (VPU) which supports the RVV scalable vector instruction set, designed from the ground up to be a Cray-like full vectorization computation unit than the incremental growth from SIMD instructions which some advanced SIMD has evolved from. As such, there is a full Vector Register File (VRF) of user-configurable number of elements per register. Each vector can be arbitrary length, from as small as 64-bit to as large as 512-bit (VLEN) and all the way to 4096-bit by combining up to eight vector registers (LMUL). It also allows each computation of integer, fixed point, floating point, and other AI-optimized representations to be any bit-width from 4 bits to 32 bits, and handles non-divisible last matrix elements in the same loop. The 27-series VPU implements all of these capabilities, and has multiple functional units which are chainable, each can operate in independent pipelines to sustain the computational throughputs needed in critical kernel functions. Fully configured, the VPU can achieve over 30x speedup measured by the key functions in MobileNets, a popular convolution neural networks (CNN). Compared to the popular 128-bit scalar SIMD solution, the NX27V VPU offers 4 times more raw processing power per cycle with additional advantage due to the higher efficiency of vector instruction issuing.

“It’s exciting to see fourteen years of R&D investment all come together in one ambitious project,” said Dr. Charlie Su. “From the vector microarchitecture to the memory subsystem, and all the ecosystems required to enable our licensees, at whatever scale and scope the licensee deems appropriate, Andes has taken RISC-V users to the frontiers of these embedded applications.”

Indeed, the 27-series has vastly expanded its memory subsystem to keep up with the bandwidth required to sustain the computational rate of the VPU, all of which will benefit all customers in general, whether they use the VPU or not. The 27-series now supports multiple outstanding memory accesses inflight so the scalar and vector processors both don’t have to wait for the data during cache misses. In addition, cache pre-fetches allow the memory to prepare data in advance of processor’s needs, thus hiding potential cache misses. Finally, Andes Custom Extension (ACE) interface has been expanded to provide instruction customization to speed up control path as well as to widen data path into the core.

Pricing and Availability:

The 27-series processor beta release has been delivered to Andes’ first licensee in early December, 2019, with production database release in Q1, 2020. Please contact Andes Sales at sales@andestech.com for configuration and pricing of the 27-series processors.

About Andes Technology

Fourteen years after starting from scratch, Andes Technology Corporation is now a world class creator of innovative high-performance/low-power 32/64-bit processor cores and associated development environment that serves the rapidly growing global market for embedded system applications. A founding Platinum member of RISC-V Foundation, Andes is the first mainstream CPU vendor that has adopted the RISC-V as the base of its fifth-generation architecture, the AndeStar™ V5. To meet the demanding requirements of today’s electronic devices, Andes delivers highly configurable and performance-efficient CPU cores with full-featured integrated development environment and comprehensive software/hardware solutions to help customers innovate their SoC in a shorter time to market. Since 2018, the yearly volume of SoCs Embedded with Andes CPUs has surpassed the 1-billion mark. Andes Technology’s comprehensive RISC-V CPU families range from the entry-level 32-bit N22, mid-range 32-bit N25F/D25F/A25 and 64-bit NX25F/AX25F, to the high-end multicore A(X)25MP.