Picocom Embeds 32 Andes N25F RISC-V Cores into Its 5G NR Small Cell Baseband SoC

- Post author:Sheila

- Post published:2020-08-04

- Post category:Press Release

HSINCHU, TAIWAN –August 4, 2020– Picocom has selected the AndesCore™ N25F RISC-V 32-bit core integrated with the AE350 peripherals platform for its forthcoming 5G small cell distributed unit (DU) System-on-Chip (SoC). Picocom is a 5G open RAN baseband semiconductor company with vast experience in the field of small cells. Its chosen partner, Andes Technology, is a leading supplier of high-performance, low-power compact 32/64-bit RISC-V CPU cores and the Founding Premier member of the RISC-V International Association.

Picocom is championing ‘open RAN’ – the disaggregation of 5G radio access networks (RAN), which will open up the supply chain enabling new vendors to enter the market and compete. With Andes performance efficient cores, Picocom’s DU baseband offload SoC will deliver the needed flexibility, efficiency and performance to meet the challenges brought by 5G small cells.

“Andes N25F 32-bit RISC-V cores are small, yet powerful. Their compact size allows Picocom to use 32 of them, in the form of two clusters, providing flexible processing for data throughputs at line rates up to 25 Gbps for packet header processing,” said Peter Claydon, President, Picocom. “Our engineering team found that using clusters of small RISC-Vs is more efficient than using a small number of larger cores. This clustered RISC-V approach enables us to retain maximum flexibility to cope with future 5G NR standards changes while delivering excellent performance in a very demanding application.”

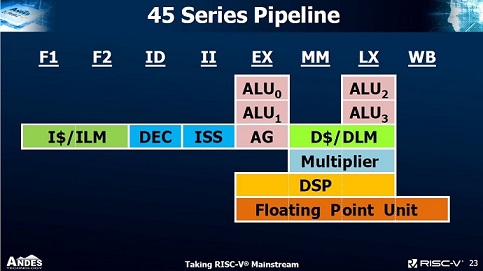

“The RISC-V core N25F is a proven outstanding solution for high-speed control tasks and floating-point intensive applications. We are delighted that Picocom recognizes the strength of N25F and utilizes dozens of them in clusters, along with the integrated Platform AE350 to design its advanced 5G small cell SoC.” said Dr. Charlie Su, CTO and Executive VP of Andes Technology. “It again validates that Andes’ RISC-V solutions are ideal to tackle the demanding requirements of high-speed protocol control with significant performance for applications such as storage, networking and wireless communication.”

About Picocom

Picocom is a semiconductor company that designs and markets open RAN standard-compliant baseband SoCs and carrier-grade software products for 5G small cell infrastructure. The company, founded in 2018, is headquartered in Hangzhou, China, and has R&D engineering sites in Beijing, China and Bristol, UK. Picocom founding members have significant experience in designing baseband infrastructure products. Picocom is a proud member of the Small Cell Forum, O-RAN Alliance and Telecom Infra Project wireless industry associations. More information about Picocom: http://www.picocom.com.

About Andes Technology

Andes Technology Corporation is a world-class creator of innovative high-performance/low-power 32/64-bit processor cores and associated development environment to serve the rapidly growing global embedded system applications. The company delivers superior low power CPU cores, including the comprehensive RISC-V V5 family of processor IPs, with integrated development environment and associated software/hardware solutions for efficient SoC design. Up to the end of 2019, the cumulative volume of Andes-Embedded™ SoCs has surpassed the 5-billion mark. Andes Technology’s comprehensive CPU line includes extensible entry-level, mid-range and high-end families. For more information, please visit http://www.andestech.com.