Andes Technology Unveils Andes D23 and N225 Cores Pioneering the Next Generation of Compact, Performant, and Secure RISC-V Processor Technology

- Post author:Lee Claire

- Post published:2023-10-18

- Post category:Press Release

Hsinchu, Taiwan – Oct. 17, 2023 – Andes Technology, the renowned supplier of high-efficiency, low-power 32/64-bit RISC-V processor cores and a Founding Premier member of RISC-V International, proudly announces the release of its latest innovation – the AndesCore™ D23 and N225 RISC-V processors. Specifically designed to cater to the dynamic needs of the Internet of Things (IoT) and embedded systems, these cores epitomize Andes’ unwavering commitment to delivering cutting-edge technology for the interconnected world.

The D23 and N225 cores have been meticulously engineered with compactness, performance-efficiency, low-power consumption, flexibility, and security as top priorities. These cores empower IoT and embedded chip and device manufacturers to meet the burgeoning demands of a rapidly evolving market while minimizing power usage and ensuring robust security.

Andes announced the popular N22, a 2-stage pipeline AndesCore implementing RV32I/EMAC ISA back in February 2019, targeting deeply embedded processing and having a performance of 3.95 Coremark/MHz and 1.8 DMIPS/MHz. The D23 and N225 are revamped designs with a new microarchitecture and the latest RISC-V extensions (details below) to offer better performance, smaller code size, and more security support. They provide a good migration path for customers looking to upgrade their N22 designs or kick-off a new design today.

Common Key Features of AndesCore D23 and N225:

Latest RISC-V Extensions Support: The N225 implements the RV32 IMACBZce non-privileged extensions as well as Machine/User modes and Enhanced Physical Memory Protection (ePMP). The D23 additionally supports the FDKP extensions (Single/Double-Precision Floating-Point, Scalar Crypto and Packed SIMD/DSP draft), and CMO (Cache Management Operations) extension. The D23 is also incorporated with Supervisor mode and its associated PMP (sPMP) for higher security.

Compact Size: Both cores feature a highly compact design with a 3-stage pipeline, primarily supporting single instruction issue with some dual-issue capability. This makes them exceptionally well-suited for space- and memory-constrained IoT and embedded applications, including wearables, sensors, and smart home devices.

High Performance: Both cores achieve industry-leading performance in their class, boasting outstanding benchmark scores such as 4.55 (D23) and 4.4 (N225) Coremark/MHz, and 2.08 (D23) and 1.92 (N225) DMIPS/MHz, respectively. They are capable of operating at high frequencies across various technology nodes such as near 800 MHz at 28nm, providing the necessary computing power for edge IoT devices with ever-increasing performance and feature demands.

Power Management: Both cores support advanced power management technologies such as PowerBrake and Wait-For-Interrupt (WFI) and Wait-For-Event (WFE), ensuring prolonged battery life for many types of untethered IoT devices.

Small Code Size: The N22 already offers industry-leading code size with Andes CoDense™ technology. With the addition of the new RISC-V Zce code size reduction extension, the D23 and N225 further reduce 4.4% code size for the Embench-IoT benchmark, compared to the N22. This provides additional memory cost-saving for Andes customers.

Flexibility: Both cores offer extensive configurability, including optimized multipliers for performance or area, optional static or dynamic branch prediction, various combinations of privilege modes, instruction and data Local Memories with sizes from 1 KB to 512 MB, and 2-wire or 4-wire JTAG debug interface. Designers can tailor these features to address their specific application requirements.

Ease of SoC Integration: To simplify integration into System-on-Chip (SoC) designs, both cores support either Core-Local Interrupt Controller (CLIC) for the single-CPU SoC or Platform-level Interrupt Controller (PLIC) for multiple-CPU SoC, rich options for AMBA interfaces, private machine timers or platform machine timers, and instruction trace interfaces.

In addition to the above-mentioned shared features and latest RISC-V extensions, the D23 core boasts additional capabilities, including built-in instruction and data caches, and ECC soft error protection for all cache and local memories. It can also seamlessly integrate with the powerful ACE™ (Andes Custom Extension) to support custom instructions for Domain-Specific Acceleration (DSA) and has a roadmap to include a functional safety derivative. These expanded capabilities open up opportunities for the D23 to serve a wider range of segments in automotive and industrial control applications.

Dr. Charlie Su, President and CTO of Andes Technology, expressed his enthusiasm for the release of these cores, stating, “The D23 and N225 mark a significant milestone in our commitment to providing innovative solutions for the IoT and embedded segments. With their compact design, power efficiency, and robust security features, these cores are poised to set new industry standards. We believe they will empower designers and developers to create cutting-edge products that can thrive in the fast-paced world of IoT.”

The D23/N225 have been licensed out and several companies are actively evaluating them. Their overall features will be developed and delivered in two phases. For more information about these cores, please visit the Andes Technology website.

About Andes Technology

Eighteen years in business and a Founding Premier member of RISC-V International, Andes is a publicly-listed company (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099) and a leading supplier of high-performance/low-power 32/64-bit embedded processor IP solutions, and the driving force in taking RISC-V mainstream. Its V5 RISC-V CPU families range from tiny 32-bit cores to advanced 64-bit Out-of-Order processors with DSP, FPU, Vector, Linux, superscalar, and/or multi/many-core capabilities. By the end of 2022, the cumulative volume of Andes-Embedded™ SoCs has surpassed 12 billion. For more information, please visit https://www.andestech.com. Follow Andes on LinkedIn, Twitter, Bilibili and YouTube!

Andes Announces General Availability of the New AndesCore™ RISC-V Multicore Vector Processor AX45MPV

- Post author:Lee Claire

- Post published:2023-09-08

- Post category:Press Release

Hsinchu, Taiwan – Sep. 7, 2023 – Andes Technology, a leading supplier of high efficiency, low-power 32/64-bit RISC-V processor cores and Founding Premier member of RISC-V International, today proudly announces general availability of the high-performance AndesCore™ AX45MPV multicore vector processor IP. The AX45MPV is the third generation of the award winning AndesCore™ vector processor series. Equipped with powerful RISC-V vector processing and parallel execution capability, it targets the applications with large volumes of data such as ADAS, AI inference and training, AR/VR, multimedia, robotics, and signal processing.

Andes and Meta started collaboration on datacenter AI with RISC-V vector core from early 2019*(See Remarks). Andes later unveiled the AndesCore™ NX27V, marking a significant milestone as the industry’s first commercial RISC-V vector processor core with the capability of generating up to 4 512-bit vector (VLEN) results per cycle, at the end of 2019. It immediately attracted the attention of worldwide SoC design teams working on AI accelerators, and has landed over a dozen datacenter AI projects. Since then, the RISC-V vector processor cores have become the choice for ML and AI chip vendors.

With the goal to further raise the compute density, the AX45MPV extends the capabilities of the dual-issue 8-stage pipeline, Linux support and multicore of the AX45MP with the powerful vector processing unit inherited and enhanced from its predecessor, the NX27V. While the AX45MPV is essentially a Linux application processor with datacenter grade AI capabilities, its support for Linux and multicore can be left out to form an efficient and powerful compute processor in processing elements (PEs) of a large compute array. The dual-issue capability combined with up to 6 1024-bit vector (VLEN) results per cycle in the AX45MPV can provide more than 3X performance comparing with its predecessor. To fully exploit its higher computation power, the AX45MPV offers two 1024-bit memory interfaces. The new high-bandwidth vector local memory (HVM) option provides 1 or 2 HVM bank ports, ideal for vector loads/stores, and an external DMA engine to move chunks of data in the background through an AXI-based HVM Access Port. For computation tasks requiring an integrated coprocessor control along with data transfer, the versatile Andes Streaming Port (ASP) available since the first Andes vector processor is the best solution. By combining the ASP and the HVM ports, the processor effectively doubles its memory bandwidth by, say, being able to load 2 vector data per cycle. The AX45MPV also supports the latest ACE (Andes Custom Extension™), which facilitates customers to create their own RISC-V styled vector instructions. For example, ACE can be used to accelerate nonlinear math functions such as SoftMax on Transformer AI.

“Andes has been serving datacenter AI customers since 2019 with RISC-V Vector architecture and has accumulated rich experience. Equipped with the powerful 1024-bit vector unit, efficient support of multicore and Linux, and versatile configurations, the third generation of Andes vector processors AX45MPV is specially tailored for Large Language Models (LLMs). With the surge of generative AI applications in 2023, we see the AX45MPV taking the center stage in AI and Machine Learning segments beyond the Cloud.”, said Dr. Charlie Su, President and CTO of Andes Technology.

Some customers from Asia and North America have already licensed the AX45MPV, and more are evaluating it. Their applications cover a wide range from the cloud to the edge. The AX45MPV standard product package, without Linux support, is available immediately. Its advanced product package will come with Linux support and will be available in Q4 2023.

About Andes Technology

Eighteen years in business and a Founding Premier member of RISC-V International, Andes is a publicly-listed company (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099) and a leading supplier of high-performance/low-power 32/64-bit embedded processor IP solutions, and the driving force in taking RISC-V mainstream. Its V5 RISC-V CPU families range from tiny 32-bit cores to advanced 64-bit Out-of-Order processors with DSP, FPU, Vector, Linux, superscalar, and/or multi/many-core capabilities. By the end of 2022, the cumulative volume of Andes-Embedded™ SoCs has surpassed 12 billion. For more information, please visit https://www.andestech.com. Follow Andes on LinkedIn, Twitter, Bilibili and YouTube! !

*Remarks: MTIA: First Generation Silicon Targeting Meta’s Recommendation Systems, ISCA ’23: Proceedings of the 50th Annual International Symposium on Computer Architecture, June 2023

GlobeNewswire – Andes Announces General Availability of the New AndesCore™ RISC-V Multicore Vector Processor AX45MPV

- Post author:Lee Claire

- Post published:2023-09-07

- Post category:News

eeNews – Andes ships RISC-V vector IP for data centre transformer AI chips

- Post author:Lee Claire

- Post published:2023-09-07

- Post category:News

GOWIN Semiconductor & Andes Technology Corp. Announce The First RISC-V CPU and Subsystem Ever Embedded 22nm SoC FPGA

- Post author:Lee Claire

- Post published:2023-08-29

- Post category:Press Release

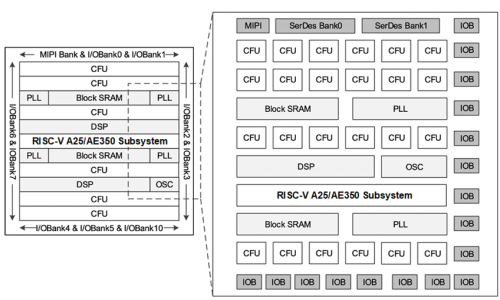

GOWIN Is Offering the Andes A25 RISC-V CPU IP and AE350 Subsystem

As Instantiated Hard Cores in Its GW5AST-138 FPGA

San Jose, CA – Aug. 29, 2023 – Andes Technology Corporation (TWSE: 6533), a leading supplier of high efficiency, low-power 32/64-bit RISC-V processor cores and Founding Premier member of RISC-V International, is thrilled to announce that its AndesCore™ A25 RISC-V CPU IP and AE350 peripheral subsystem is hardened and embedded in the GW5AST-138 FPGA chip from GOWIN Semiconductor, the world’s fastest growing FPGA company. This integration, one of the first complete RISC-V microcontrollers in an FPGA, provides designers the A25 processor power and the peripherals most processors require without consuming any FPGA resources. Thus, the hardware team can populate the FPGA with their value-added design while the software team can concurrently create application code based on the rich RISC-V ecosystem.

“Andes is committed to delivering cutting-edge RISC-V technologies allowing developers to create innovative and efficient solutions. The integration of the A25 RISC-V CPU and AE350 peripheral subsystem as a hard core in GOWIN Semiconductor’s GW5AST-138 FPGA marks a significant milestone in achieving this vision,” said Andes North America VP of Sales, Vivien Lin. “This represents a significant milestone for the RISC-V architecture as it provides our joint customers a versatile hardware development platform to create, debug, and verify their ultimate SoC design before committing their netlist for silicon fabrication. For customers not requiring an SoC, it will enable a complete RISC-V computer ready to drive their end applications.”

“In the Arora V family, we incorporate the peripherals that a RISC-V CPU typically requires in hard instantiations,” says GOWIN’s Sr. Director of Solution Development, Jim Gao. “We included a fully controllable high-speed SerDes for communication, video aggregation, and AI computing acceleration applications that demand very high data rates. Other instantiated functions include Block RAM modules supporting ECC error correction, high-performance multiple voltage GPIO, and high accuracy clock architecture. These hard functions save the FPGA programmable fabric of up 138K LUT’s for the designers’ unique logic implementation.”

About the RISC-V Based GW5AST-138 FPGA:

The AndesCore™ A25 hard core, running at 400MHz, supports the RISC-V P-extension DSP/SIMD ISA (draft), single- and double-precision floating point and bit-manipulation instructions, and MMU for Linux based applications. The AE350 AXI/AHB-based platform comes with level-one memories, interrupt controller, debug module, AXI and AHB Bus Matrix Controller, AXI-to-AHB Bridge and a collection of fundamental AHB/APB bus IP components pre-integrated together as a system design. DDR3 controller and SPI-Flash controller in the FPGA fabric back up the A25’s 32KByte I-Cache and D-Cache after cache misses. Off chip DDR3 provides data memory, SPI-Flash contains the A25’s instruction memory (codes copied from SPI-Flash into DDR3 and Cache upon boot-up). Besides hard instantiated functions, the GOWIN GW5AST-138 FPGA fabric affords 138K LUTs for custom design implementation. GOWIN EDA provides an easy-to-use FPGA hardware development environment for the Arora V. The environment supports multiple RTL-based programming languages, synthesis, placement and routing, bitstream generation and download, power analysis and in-device logic analyzer.

Price & Availability

The GW5AST-138 FPGA with SDK with GOWIN_V1.9.9 Beta-3 will be available August 18 through distribution.

About GOWIN Semiconductor Corp.

Founded in 2014, GOWIN Semiconductor Corp., headquartered with major R&D in China, has the vision to accelerate customer innovation worldwide with our programmable solutions. We focus on optimizing our products and removing barriers for customers using programmable logic devices. Our commitment to technology and quality enables customers to reduce the total cost of ownership from using FPGA on their production boards. Our offerings include a broad portfolio of programmable logic devices, design software, intellectual property (IP) cores, reference designs, and development kits. We strive to serve customers in the consumer, industrial, communication, medical, and automotive markets worldwide.

About Andes Technology

Eighteen years in business and a Founding Premier member of RISC-V International, Andes is a publicly listed company (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099), a leading supplier of high-performance/ low-power 32/64-bit embedded processor IP solutions, and the driving force in taking RISC-V mainstream. Its V5 RISC-V CPU families range from tiny 32-bit cores to advanced 64-bit Out-of-Order processors with DSP, FPU, Vector, Linux, superscalar, and/or multi/many-core capabilities. By the end of 2022, the cumulative volume of Andes-Embedded™ SoCs has surpassed 12 billion. For more information, please visit https://www.andestech.com. Follow Andes on LinkedIn, Twitter, Bilibili and YouTube!

GlobeNewswire – GOWIN Semiconductor & Andes Technology Corp. Announce The First Ever RISC-V CPU and Subsystem Embedded 22nm SoC FPGA

- Post author:Lee Claire

- Post published:2023-08-29

- Post category:News

Andes Technology and TetraMem Collaborate to Build Groundbreaking AI Accelerator Chip with Analog In-Memory Computing

- Post author:Lee Claire

- Post published:2023-08-11

- Post category:Press Release

San Jose, CA – Aug 10, 2023 – Andes Technology, a leading supplier of high-efficiency, low-power 32/64-bit RISC-V processor cores and Founding Premier member of RISC-V International, and TetraMem Inc, a pioneer in analog memristor technology and in-memory computing, are proud to announce a strategic partnership aimed at delivering a fast, highly efficient, AI inference chip that will revolutionize the landscape of artificial intelligence and edge computing.

The convergence of AI and edge computing has become a driving force behind the advancement of numerous industries, including autonomous vehicles, smart cities, healthcare, cybersecurity, and entertainment. Recognizing the immense potential of this market, TetraMem has licensed the powerful Andes RISC-V NX27V vector CPU, combined with ACE (Andes Custom ExtensionTM) to create a cutting-edge solution that addresses the challenges of AI processing in power-constrained environments.

The centerpiece of this collaboration is the fusion of Andes’ high-performance RISC-V Vector CPU with TetraMem’s revolutionary compute memristor – an analog RRAM – in-memory computing architecture through ACE to enable tight coupling for the best performance. This unprecedented combination amplifies the strengths of both companies, resulting in blazingly fast, energy-efficient AI inference that surpasses the limitations of traditional computing approaches – transcending “memory wall” and “end of Moore’s Law” constraints.

Features of the AI Accelerator Chip:

1. RISC-V Vector CPU Excellence: Andes RISC-V Vector CPU cores are known for their exceptional performance, efficiency, and configurability, making them ideal for a wide range of AI and edge computing applications. The addition of Andes powerful vector processor brings unparalleled performance capabilities to the accelerator chip.

2. Analog In-Memory Computing Prowess: TetraMem’s unique, analog in-memory computing technology empowers the chip with massively parallel VMM computation without data movement, mitigating the energy overhead of conventional architectures as confirmed in TetraMem’s first commercially manufactured demonstration chip.

3. Energy-Efficient AI Acceleration: The joint effort aims to create a chip that is not only powerful but improves energy-efficient by at least an order of magnitude. By optimizing computations and eliminating transfer of weight data, the planned chip will significantly extend the battery life of edge devices and impose a near-zero impact on thermal budgets.

4. Flexible and Scalable: The AI accelerator chip will be designed from 22nm and beyond, to 7nm and below in the future, with versatility and scalability in mind for easy integration into various AI-powered products and applications. This adaptability ensures broad industry applicability. The TetraMem founding team has demonstrated scalability of the compute memristor to 2nm and below, ensuring a roadmap to future-proof solutions.

Mr. Frankwell Lin, Chairman and CEO of Andes Technology, expressed his enthusiasm for the partnership, saying, “Our collaboration with TetraMem represents a significant milestone in the advancement of AI accelerators. By combining Andes’ world-class RISC-V vector processing technology with TetraMem’s groundbreaking analog in-memory computing, we are poised to deliver a revolutionary solution that will empower the next generation of AI applications.”

Dr. Glenn Ning Ge, CEO of TetraMem Inc,, echoed this sentiment, stating, “TetraMem’s analog-RRAM-based in-memory computing technology changes the physics of how AI computations are performed, launching a new era in computing. Working hand in hand with Andes, we are confident that our joint AI accelerator chip will set a new standard for AI processing in terms of speed and energy efficiency.”

Tetramem anticipates unveiling the AI accelerator chip and making engineering samples and development kits for the new 22nm “TetraMem MX Series” chip available to the public by the second half of 2024. The partnership between Andes and TetraMem signifies a major leap forward in the field of AI hardware, promising to unlock unprecedented possibilities for AI innovations.

For more information about Andes Technology and TetraMem Technologies, please visit their respective websites at www.andestech.com and www.tetramem.com.

About Andes Technology

Eighteen years in business and a Founding Premier member of RISC-V International, Andes is a publicly-listed company (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099) and a leading supplier of high-performance/low-power 32/64-bit embedded processor IP solutions, and the driving force in taking RISC-V mainstream. Its V5 RISC-V CPU families range from tiny 32-bit cores to advanced 64-bit Out-of-Order processors with DSP, FPU, Vector, Linux, superscalar, and/or multi/many-core capabilities. By the end of 2022, the cumulative volume of Andes-Embedded™ SoCs has surpassed 12 billion. For more information, please visit https://www.andestech.com. Follow Andes on LinkedIn, Twitter, Bilibili and YouTube!

About TetraMem Inc

Founded in 2018 by a team of world-class experts, TetraMem is poised to deliver the industry’s most disruptive in-memory computing (IMC) technology for edge applications. The TetraMem team brings together complementary skill sets and technological know-how with 34 patents granted to date spanning materials science, device, circuit design, architecture, and application, as well as a patented six-dimension co-design methodology. TetraMem is the world’s only company to produce a high bit-density multi-level memristor-based accelerator in a commercial foundry, with the technology featured in the March 30, 2023 edition of the journal, Nature. This groundbreaking technology enables memory-based computation, eliminating weight-data movement, substantially improving the energy efficiency and performance of AI and machine learning workloads compared to digital technologies, with scalability well beyond the limits of competing analog technologies. For more information, please visit https://www.tetramem.com. Follow TetraMem on LinkedIn.

GlobeNewswire – Update: Andes Technology and TetraMem Collaborate to Build Groundbreaking AI Accelerator Chip with Analog In-Memory Computing

- Post author:Lee Claire

- Post published:2023-08-10

- Post category:News

Terapines ZCC Toolchain Fully Supports Andes RISC-V Processors

- Post author:Lee Claire

- Post published:2023-07-31

- Post category:Press Release

Wuhan, China – July 31, 2023 – Terapines Technology, an innovative provider of software/hardware co-design solutions announces the full support for Andes RISC-V processors lineup in the Terapines ZCC toolchain. The ZCC toolchain delivers proven performance gains across multiple end markets, including embedded systems, high-performance computing, and AI. Andes Technology Corporation (TWSE: 6533), a leading supplier of high efficiency, low-power 32/64-bit RISC-V processor cores and Founding Premier member of RISC-V International, has been instrumental in driving RISC-V into the mainstream. Recently, Terapines Technology has joined RISC-V International as a Strategic Member, enabling closer collaboration between these two companies and the overall RISC-V community.

The full support of ZCC toolchain for AndeStar™ V5 Instruction Set Architecture will allow Andes and its silicon partners to achieve higher code density and performance for MCU and SoC products built on the V5 architecture. It opens the door to optimized RISC-V implementations across a wider range of applications.

The benchmark results demonstrate the ZCC toolchain’s ability to optimize the system performance versus LLVM from AndeSight™ IDE. Based on AndesCore™ AX45 CPU, ZCC achieved a 6% boost over the baseline on CoreMark score, as well as an 18.9% performance improvement and 11.8% better code density on Embench-IoT (-O3). With -Os optimization, Embench-IoT attained a 10% code density gain and 9.1% faster performance.

On the industry-standard SPECInt2006 benchmark, ZCC delivered a 30% lower dynamic instruction count compared to open-source LLVM 16.0 on a RV64GCBV RISC-V processor. It also achieved a 13% lower dynamic instruction count on a RV64GCB RISC-V processor.

These gains showcase the potential of the ZCC toolchain to help engineers maximize efficiency and real-world speedup across a wide variety of RISC-V implementations.

Benchmark results also highlight the powerful auto-vectorization capabilities of ZCC toolchain for AI chip development. ZCC achieved up to 91x higher performance versus open-source compilers on popular computing kernel functions. In some cases, the auto-vectorized output even matched or exceeded hand-optimized assemblies in both performance and efficiency.

These exceptional auto-vectorization results mean ZCC can substantially accelerate AI chip design and lower software maintenance costs. By reducing the need for time-consuming manual optimization of computational kernels, ZCC provides a streamlined path to deploying high-throughput AI accelerators.

“Full support for AndeStar™ V5 ISA in the ZCC toolchain is just the starting point of our collaboration with Andes,” said Hualin Wu, CTO of Terapines Technology. “We look forward to deepening our partnership to further boost the performance and efficiency of Andes RISC-V processors. Beyond the toolchain, Terapines will provide Andes’ customers with access to our full suite of co-design tools and virtual prototype simulators. This will enable rapid and cost-effective design flow of competitive RISC-V chips optimized for their target applications.”

“This collaboration between Terapines and Andes to optimize RISC-V processor performance and code density will greatly benefit our mutual customers,” said Dr. Charlie Su, President and CTO of Andes Technology. “As RISC-V continues its rapid growth, expanding the ecosystem with professional tools like ZCC is crucial for ensuring customer product competitiveness. We look forward to broadening our collaboration to equip designers with the best-in-class solutions needed to maximize the potential of RISC-V.”

About Terapines

Founded in late 2019, Terapines Technology specializes in developing RISC-V software/hardware co-design toolchain. With optimized compilers and simulators as core technologies, Terapines offers products and solutions across four key areas: software/hardware co-design and co-verification, functional safety checker, DSA and embedded development, and ROS operating systems. To learn more about Terapines’ innovative RISC-V solutions, follow our WeChat official account or visit https://www.terapines.com

About Andes Technology

Eighteen years in business and a Founding Premier member of RISC-V International, Andes is a publicly-listed company (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099) , a leading supplier of high-performance/ low-power 32/64-bit embedded processor IP solutions, and the driving force in taking RISC-V mainstream. Its V5 RISC-V CPU families range from tiny 32-bit cores to advanced 64-bit Out-of-Order processors with DSP, FPU, Vector, Linux, superscalar, with processor integrating vector processor and/or multi/many-core capabilities. By the end of 2022, the cumulative volume of Andes-Embedded™ SoCs has surpassed 12 billion. For more information, please visit https://www.andestech.com. Follow Andes on LinkedIn , Twitter, Bilibili and YouTube!