The exponential growth of smart device markets such as IoT and home automation appliances requires SoC designs to deliver high performance at minimum cost and low power consumption. To help designers address the challenge, the Andes Custom Extension™ (ACE) is invented for customers to add their own instructions to AndesCore™ processors. By combining highly performance efficient baseline features of AndesCore™ with the ACE instructions tailored for customers’ applications, SoCs can get the benefits from both sides: the complete flexibility of processor programmability and the absolute efficiency of hardwired engine.

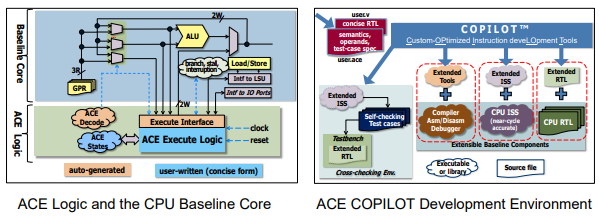

Users define ACE instruction first by profiling their C programs on Andes ISS simulator to identify the code segments which contribute to significant percentage of execution time. Those code segments then can become part of the instruction semantics in an ACE description file. The file also specifies the instruction mnemonic, the operand(s) and the estimated amount of cycle(s) to execute in hardware. Substituting the original code with ACE intrinsic functions which are automatically generated to represent the corresponding ACE assembly instructions, the application software can be profiled again to get the estimated performance improvements. If the results are satisfiable, user can go ahead to design the Verilog RTL representing the same functionality as the instructions. The Verilog is in a concise format which consists of only the execution logic while the manual work for connections to the CPU pipeline are not required. The ACE description file and concise Verilog file are all that customers need to design for ACE’s development environment.

The Custom-OPtimized Instruction deveLOpment Tools (COPILOT™) parses ACE description file and generates the shared libraries needed for the toolchain to recognize ACE instructions. It also parses the concise Verilog RTL and generates the complete extended ACE Verilog module to connect to the CPU pipeline. Then a new processor equipped with custom instructions is ready for SoC integration and software development. The simplicity of ACE and COPILOT™ environment allows user to focus on ACE instruction’s functionality itself without worrying about housekeeping functionality in the CPU pipeline. In addition, using the extended toolchain is the same as standard tools. Since the extended components are all generated locally, the light-weight flow lets users easily try out as many experiments as they need.

Deblocking filter is a computation intensive function used for improving visual quality by eliminating the blocking artifact introduced during video encoding. It can be optimized by defining the ACE instructions that implements data manipulation functions for performance, and leaving the control tasks in the software for flexibility. The performance, power and area (PPA) benchmark shows stunning results as ACE boosts performance by running 102 times faster, but consumes only 1/74 of the power.

ACE descriptions in C and Verilog enable high level behaviors to be implemented in a single instruction. For example by encapsulating hardware operators with loop semantics, ACE instructions can repeat their operations for a variable iteration count by itself. This is possible because ACE allows instructions to be single or multi cycles, fixed or variable cycles. With this high level construct, the repeated instruction fetches and decodes are eliminated. Therefore both performance and power consumption are greatly improved.

In addition to performance, power and cost, security for the software IP is another major concern for designers of intelligent devices. By converting C code segments into ACE instructions, design’s proprietary functionalities are concealed in hardware so that reverse engineering the program code will not reveal that information. Furthermore, since the ACE design flow is conducted completely within users’ computer, not required to be submitted over Internet to vendor’s server, the confidentiality of the design can be secured.

Andes Technology Corporation offer customers the instruction extension capability with the belief that every design is unique, and by enabling them to accelerate their own application-specific functions on the general-purpose processors, their applications will run more efficiently, and their products will be more competitive. On the contrary, some processor vendors keep tight control of their instruction set and do not allow users’ own addition, eventually it will be at their customers’ expense to migrate to higher performance cores.

Today’s SoC designers are confronted with the challenges to catch up with the dynamics of process technology advancements, industry standard revisions, fierce market competitions, and more. ACE brings programmable acceleration to SoC designs by boosting performance and power efficiency while maintaining programmability. It allows users to focus on the design rather than on the tools, to implement high-level functions as instructions, and above all, to protect software IP by hardware encapsulation. All those benefits offered by ACE together assist SoC designers to conquer the challenges of ever increasing complexity in today’s embedded systems.