Munich, Germany – March 27, 2024 – TASKING proudly announces that its ISO 26262 (functional safety) and ISO/SAE 21434 (cybersecurity) compliant compilers now fully support the Andes FuSa certified RISC-V IP. This advancement expands TASKING’s RISC-V tool suite to include compilation, debugging, performance tuning, timing, and coverage analysis tools, providing a comprehensive solution for automotive systems development.

This milestone signifies a significant stride in empowering SoC design teams and automotive software developers to craft highly optimized and certifiable RISC-V based solutions. The newly introduced RISC-V compiler, compliant with ASIL D standards, seamlessly supports both current and forthcoming FuSa certified Andes RISC-V cores. Noteworthy is the compiler’s adaptability to the RISC-V ISA and its extensions, including Andes-specific extensions, ensuring dynamic optimization tailored to the target device, thereby enhancing efficiency and performance.

Andes Technology has achieved remarkable milestones in the automotive market with the introduction of the world’s first RISC-V ISO-26262 fully compliant core, N25F-SE, in 2022. Subsequently, Andes is about to unveil the ASIL-B certified D25F-SE equipped with the RISC-V SIMD/DSP P-extension support (draft), enabling efficient processing of multiple data in a single instruction. Looking ahead, Andes is set to launch processors meeting the ASIL-D standard, including the compact and secure D23-SE, the high-performance D45-SE, and the forthcoming ADAS-capable core in AX60 Series. These advancements underscore Andes’ ability to provide tailored solutions for diverse automotive applications, highlighting its leading expertise in the automotive RISC-V IP market.

“AndesCore™ RISC-V IP, certified with ISO 26262, presents a solid portfolio of automotive processor solution offering unparalleled level of flexibility and efficiency benefits to silicon development,” said Samuel Chiang, Deputy Marketing Director of Andes, “Our partnership with Tasking enables customers in the automotive industry to expedite their development processes, enhancing the performance and robustness of safety-critical RISC-V applications.”

Commenting on the collaboration, Gerard Vink, TASKING’s RISC-V lead, expressed enthusiasm, stating, “We are thrilled to collaborate with Andes and their ecosystem partners. The seamless interoperability of our tools with Andes RISC-V IP across development platforms ranging from virtual prototype to silicon implementations underscores our commitment to providing comprehensive lifecycle support for SoC development teams. Leveraging TASKING’s advanced FuSa and Cybersecurity processes, our users can fast-track compliance efforts, accelerating the time-to-market of RISC-V based automotive software solutions.”

About Andes Technology

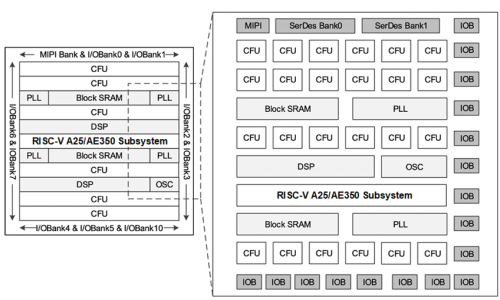

Nineteen years in business and a Founding Premier member of RISC-V International, Andes is a publicly-listed company (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099), a leading supplier of high-performance/ low-power 32/64-bit embedded processor IP solutions, and the driving force in taking RISC-V mainstream. Andes’ fifth-generation AndeStar™ architecture adopted the RISC-V as the base. Its V5 RISC-V CPU families range from tiny 32-bit cores to advanced 64-bit Out-of-Order processors with DSP, FPU, Vector, Linux, superscalar, functional safety, and/or multicore capabilities. By the end of 2023, the cumulative volume of Andes-Embedded™ SoCs has surpassed 14 billion. For more information, please visit https://www.andestech.com. Follow Andes on LinkedIn, Facebook, X, Bilibili and YouTube!

About TASKING

TASKING is a leading provider of development tools headquartered in Munich, Germany, offering high-performance, high quality, safety & security-oriented embedded software development tools for multi-core architectures.,

TASKING’s development tools are used by automotive manufacturers and suppliers, as well as in adjacent markets around the world to realize high-performance applications in safety-critical areas.

The TASKING Embedded Software Development solutions provide an industry-leading ecosystem for your entire software development process. Each TASKING compiler is designed for a certain architecture and meets the specific requirements of your industry, including automotive, industrial, telecommunications and datacom.

As the recognized leader in high-quality, feature- and safety-compliant embedded software development tools, TASKING enables you to create code with best-in-class size and performance with compilers, debuggers and RTOS support for industry-leading microprocessors and microcontrollers.

Since February 2021, TASKING has been majority-owned by financial investor FSN Capital, which has put the group on a long-term growth path following a successful carve-out. For more information visit www.tasking.com or follow us on https://www.linkedin.com/company/tasking-inc.