Home | 产品与解决方案 | AndesCore™ Processors | RISC-V: A45MP

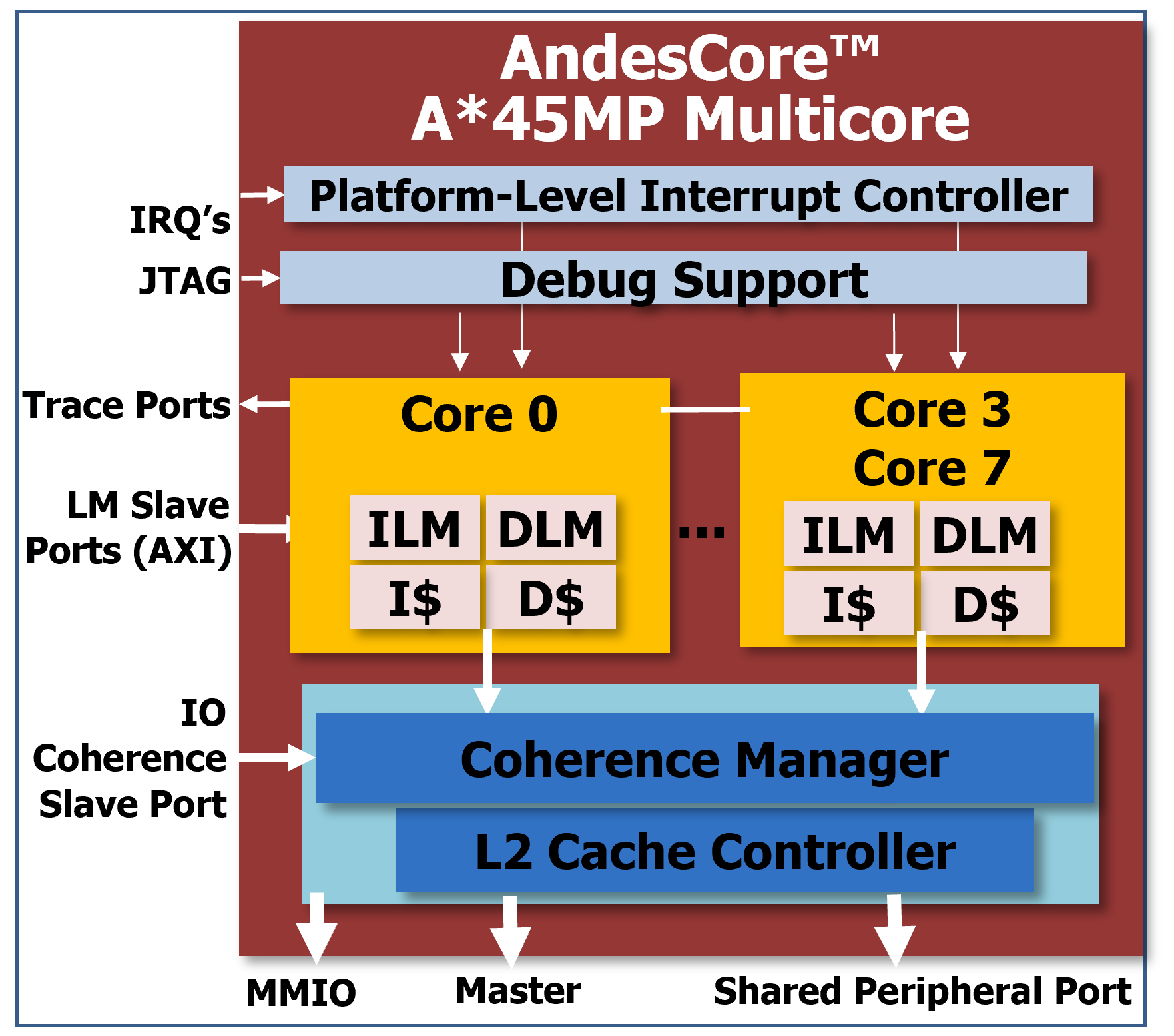

AndesCore™ A45MP Multicore

32-bit Multiprocessors with Level-2 Cache-Coherence

AndesCore™ A45MP Overview

- 32-bit, 8-stage in-order superscalar pipeline CPU architecture

- Symmetric multiprocessing up to 4 cores

- Level-2 cache and cache coherence support

- Compliant to RISC-V RV32 GCP little endian:

- RV-GC: Integer, single/double precision floating point and 16-bit extensions

- RV-P DSP/SIMD extensions (draft)

- Andes V5 performance/code size extensions

- Separately licensable Andes Custom Extension™ (ACE) for custom acceleration

- 16/32-bit mixable instruction format for compacting code density

- Branch prediction to speed up control code

- Return Address Stack (RAS) to speed up procedure returns

- Memory Management Unit (MMU), Physical Memory Protection (PMP) and Programmable Physical Memory Attributes (PMA)

- Level-1 and level-2 cache controllers with 64-byte cache line size

- MemBoost for heavy memory transactions

- Flexibly configurable Platform-Level Interrupt Controller (PLIC) for supporting wide range of system event scenarios

- Enhancement of vectored interrupt handling for real-time performance

- Advanced CoDense™ technology to reduce program code size

AndesCore™ A45MP 32-bit multicore CPU IP is an 8-stage superscalar processor based on AndeStar™ V5 architecture. It supports RISC-V standard “G (IMA-FD)” extensions, “C” 16-bit compression instructions, DSP/SIMD ‘P’ extension (draft), and Andes performance/ functionality enhancements for faster memory accesses and branch handling, plus Andes Custom Extension™ (ACE) to add user-defined instructions. It features MMU for Linux based applications, branch prediction for efficient branch execution, level-1 instruction/data caches and local memories for low-latency accesses.

The A45MP symmetric multiprocessor supports up to 4 cores and a level-2 cache controller with instruction and data prefetch. It manages level-2 cache coherence including I/O coherence for cacheless bus masters.

Other A45MP features include ECC for level-1/2 memory soft error protection, PLIC with enhancements for vectored dispatch and priority-based preemption, CoDense™ and StackSafe™ for software quality improvement,and suspend to standby/memory, CPU HotPlug, PowerBrake, and WFI for power management.

Development Tools

- AndeSight™ IDE (Eclipse-based)

- Compiler, Debugger, Profiler, Register Bit-field Display/Update, RTOS Awareness, and more

- Tested platforms: Windows and Linux, single- or multi-user installation

- Andes BSP

- Optimized DSP library

- Demo examples and sample projects

- RTOSes

- Open-source: FreeRTOS, Zephyr, RT-Thread

- Commercial: ThreadX, μC/OS-II

- SMP Linux kernel and platform drivers

- COPILOT: Custom-OPtimized Instruction deveLOpment Tool for ACE

- FPGA Development Boards

- AndeShape™ ADP-XC7K410

- Debugging Hardware

- AICE-MICRO and AICE-MINI+

Key Features and Performance

AndeStar™ V5 Architecture

| Key Features | Benefits |

|---|---|

| RISC-V RV32GCP instructions |

|

| Andes Extended Instructions | Andes exclusive performance and functionality enhancements |

| Andes Custom Extension™ (ACE) option to create custom instructions for software acceleration |

|

| 16/32-bit mixable instruction format | For compact code density |

| 32 general-purpose registers | For better code size and performance |

| Machine (M), User (U) and Supervisor (S) Privilege levels | For Linux and advanced operating systems with protection between kernel and user programs |

CPU Core

| Key Features | Benefits |

|---|---|

| 5.67 Coremark/MHz, 2.86 DMIPS/MHz* | Superior performance-per-MHz |

| 8-stage in-order superscalar pipeline | Superior performance-efficiency, while allowing for high speeds |

Extensive branch predication features

|

|

MMU (Memory Management Unit)

|

|

| Physical Memory Protection (PMP), configurable up to 32 regions | Basic read/write/execute memory protection with minimum cost |

| Programmable Physical Memory Attribute (PMA), configurable up to 16 regions | Configurable memory attributes:

|

| Performance monitors | Program code performance tuning |

| StackSafe™ hardware stack protection |

|

Multiplier options

| Option to choose between speed and area according to application's requirements |

| PowerBrake technology | Performance throttling to digitally reduce power consumption |

Cluster power management

| Different low power modes for different use cases |

* BSP v5.1.0, DMIPS/MHZ follow Dhrystone’s no-inline ground rules, best performances

Memory Subsystems

| Key Features | Benefits |

|---|---|

Level-1 I-Cache & D-Cache

|

|

Level-2 I/D Unified Cache

|

|

ILM & DLM

|

|

| MemBoost | Optimize cache reads and writes to achieve higher bandwidth and lower latency |

| Optional ECC error protection with SRAM interface | Code and data integrity protection |

| Bus master port: AXI with 128/256-bit data bus | High throughput with wide data path |

| BUS Slave Port: AXI with 128/256-bit data, for ILM/DLM accesses | Efficient data transfer between CPU and SoC masters |

| Core/bus clock ratio of N:1 | Simplified SoC integration |

Multicore Cache Coherence

| Key Features | Benefits |

|---|---|

|

|

Platform-Level Interrupt Controller (PLIC)

| Key Features | Benefits |

|---|---|

Implements RISC-V PLIC specification

| Allow individual interrupts to be serviced and prioritized without sharing |

Enhanced interrupt features

|

|

Debug Support

| Key Features | Benefits |

|---|---|

| Implements RISC-V debug specifications ver 0.13 | Supported by industry debug tool suppliers |

| JTAG Debug Port | Industry-standard support |

| Embedded Debug Module with up to 8 triggers | Flexible configurations to tradeoff between gate count and debugging capabilities |

| Exception redirection support | Entering debugger upon selected exceptions without using breakpoints |

Trace Support

| Key Features | Benefits |

|---|---|

| Implements RISC-V Trace 1.0 Instruction Trace Interface | Supported by Andes tools |

Product Package

AndesCore™ A45MP MultiCore Processor with AE350 Platform