AndesCore™ N22 Overview

- AndeStar™ V5/V5e Instruction Set Architecture (ISA), compliant to RISC-V technology

- Support RV32IMAC/EMAC

- Andes extensions, architected for performance and functionality enhancements

- 32-bit, 2-stage pipeline CPU architecture

- 16/32-bit mixable instruction format for compacting code density

- Branch predication to speed up control code

- Configurable Multipiler

- Physical Memory Protection (PMP)

- Core-Local Interrupt Controller (CLIC) with selective vectoring and priority preemption

- Flexibly configurable Platform-Level Interrupt Controller (PLIC) for supporting SoC with multiple processors

- Advanced CoDense™ technology to reduce program code size

- StackSafe™ hardware to help measuring stack size, and detecting runtime overflow/underflow

- Several configurations to tradeoff between core size and performance requirements

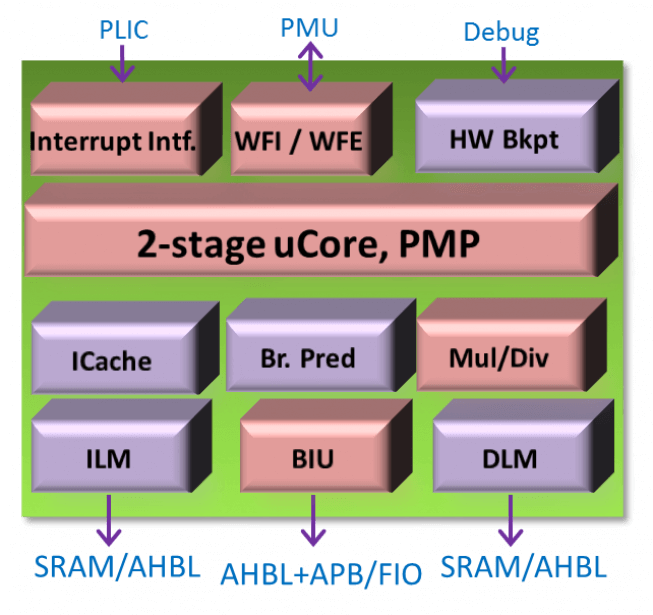

AndesCore™ N22 is a 32-bit 2-stage pipeline CPU IP core based on AndeStar™ V5 architecture for embedded applications that require low energy consumption and small area. It is compliant to RISC-V technology with several efficient performance features, including simple dynamic branch prediction, instruction cache, and local memories. It supports 32 or 16 general purpose registers (GPRs) and fast or small multiplier for performance/area tradeoff. In addition, it comes with rich optional features to ease SoC integration such as vectored CLIC and PLIC for design flexibility, AHB-Lite 32-bit bus for system integration, Fast I/O interface for low latency accesses, APB for CPU local peripherals, PowerBrake and WFI/WFE mode for low power and power management, and JTAG debug interface for development support.

Development Tools

- AndeSight™ Integrated Development Environment

- ICE debugging hardware

Key Features and Performance

AndeStar™ V5 Architecture

| Key Features | Benefits |

|---|---|

| RISC-V RV32IMAC Instructions |

|

| Andes Extended Instructions | Andes exclusive performance and functionality enhancements |

| 16/32-bit mixable instruction format | For compact code density |

| 16 or 32 general-purpose registers | For better code size and performance |

| Machine (M) and User (U) Privilege levels | Embedded systems with privilege protections |

CPU Core

| Key Features | Benefits |

|---|---|

| 1.80 DMIPS/MHz, 3.97 CoreMark/MHz* | Superior performance-per-MHz |

| 2-stage pipeline | Compact size for many applications |

| Static or dynamic branch predication | Speed up branch control codes |

| Physical Memory Protection (PMP), 16 regions | Basic read/write/execute memory protection with minimum cost |

| Performance monitors | Program code performance tuning |

| StackSafe™ hardware stack protection |

|

Multiplier options

| Option to choose between speed and area according to application's requirements |

Power Management

| Performance throttling to digitally reduce power consumption WFI instruction and WFE CSR for software power control |

* BSP v5.0.0 mculib-v5 compiler, following Dhrystone’s no-inline rules

Memory Subsystems

| Key Features | Benefits |

|---|---|

I-Cache

|

|

I/D Local Memory

|

|

Bus interfaces

| Key Features | Benefits |

|---|---|

AHB-Lite

|

|

Core-Local Interrupt Controller (CLIC)

| Key Features | Benefits |

|---|---|

| Up to 1005 interrupt sources, and up to 255 interrupt priority levels | Allow core local interrupts to be serviced and prioritized without sharing |

| Enhanced interrupt features Selective vectoring with priority preemption Support for software-based tail chaining |

|

Platform-Level Interrupt Controller (PLIC)

| Key Features | Benefits |

|---|---|

Implements RISC-V PLIC specification

| Interrupt handling for SoC with multiple processors |

Enhanced interrupt features

| Complete hardware preemption support |

Debug Support

| Key Features | Benefits |

|---|---|

| Implements RISC-V debug specifications | Supported by industry debug tool suppliers |

| JTAG Debug Port | Industry-standard support |

| Embedded Debug Module with up to 8 triggers | Flexible configurations to tradeoff between gate count and debugging capabilities |

| Exception redirection support | Entering debugger upon selected exceptions without using breakpoints |

Performance

| Core, Process | N22, 28HPC+ |

|---|---|

| Frequency (MHz) | 50 |

| Dynamic power (uW/MHz) | 2.42 |

| Area (mm2) | 0.009 |

| Core, Process | N22, 28HPC+ |

|---|---|

| Frequency (MHz) | 700 |

| Dynamic power (uW/MHz) | 4.6 |

| Area (mm2) | 0.013 |

* Base configuration, SVT 9-track library, SS corner, 0.81V, -40°C, and with I/O constraint. Power consumption at TT corner, 0.9V, 25°C

Standard Product Package

- AndesCore™ N22 with CPU Subsystem

- Pre-integrated N22, PLIC, Debug Module, and simulation-only encrypted Standard AE250 Platform

- AndesCore™ N22 with Standard AE250 AHB Platform

FreeStart Product Packages

- AndesCore™ N22 with with Encrypted FreeStart AE250 Platform

- AndesCore™ N22 with FreeStart AE250 AHB Platform