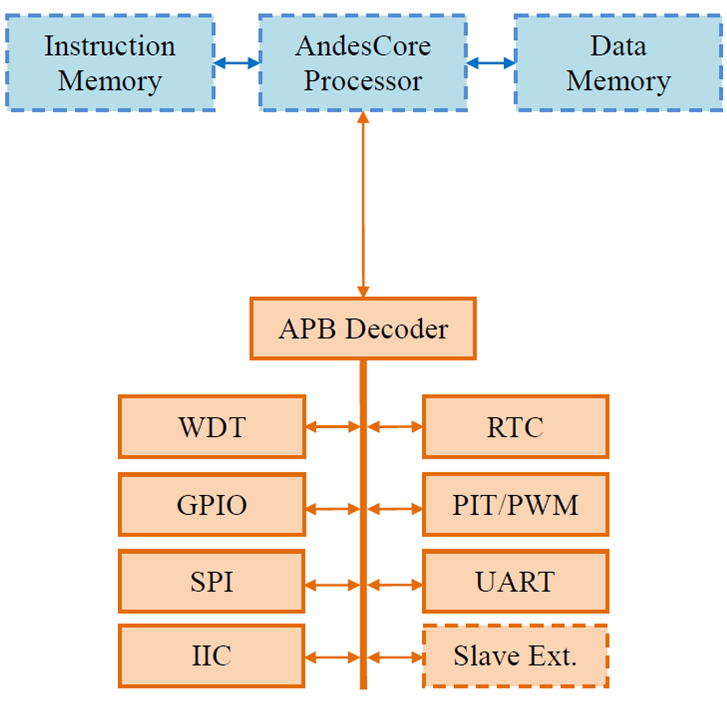

General Description

AE210P is a generic SoC platform IP which provides users with high flexibility, low cost and fast time to market for micro-controller applications such as Internet of Things (IoT) and Wearable Computing. To minimize the cost, the bus structure of AE210P can be simplified to one APB only. To maximize the performance, AE210P can be configured to add an AHB bus matrix. All the bus controllers, bridges, and peripheral IPs of AE210P are designed to minimize the access latency, the logic gate count, and the power consumption. Through the provided interfaces, users’ designs can be easily integrated to the platform.

Feature Highlight

Bus Controller / Bridge

- AHB Bus Matrix Controller (BMC)

- AHB-to-APB Bridge (APBBRG)

- APB Decoder (APBDEC)

APB Bus Components

- UART Controller

- SPI Controller

- I2C Controller (IIC)

- GPIO

- Timer (PIT) / PWM

- Watchdog Timer (WDT)

- Real Time Clock (RTC)

AHB Bus Components

- DMA Controller (DMAC)

- Local Memory Bridge (LMBRG)

Architecture

- Supports AndesCore™ N7/N8/N9/N10

- Provides two bus structures

- APB-only

- AHB bus matrix with APB

- Provides interfaces for design extension/integration

- AHB master/slave interfaces

- APB slave interface

- Interrupt signals

- DMA handshake