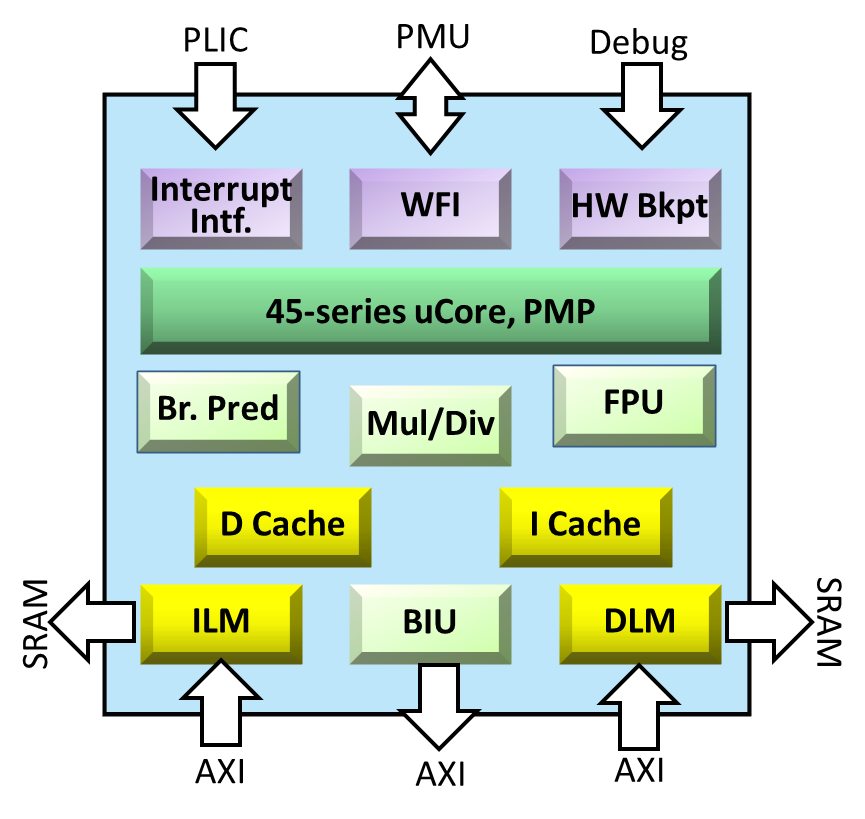

AndesCore™ NX45 Overview

- 64-bit in-order dual-issue 8-stage pipeline CPU architecture

- AndeStar™ V5 Instruction Set Architecture (ISA)

- Compliant to RISC-V RV64 GCBP little endian:

- RV-GC: Integer, single/double precision floating point and 16-bit extensions

- RV-B Bit manipulation extensions

- RV-P (draft) DSP/SIMD extensions

- Andes V5 performance/code size extensions

- 16/32-bit mixable instruction format for compacting code density

- Advanced low power branch predication to speed up control code

- Return Address Stack (RAS) to accelerate procedure returns

- Physical Memory Protection(PMP), and programmable Physical Memory Attribute (PMA)

- MemBoost for heavy memory transactions

- Flexibly configurable Platform-Level Interrupt Controller (PLIC) for supporting wide range of system event scenarios

- Enhancement of vectored interrupt handling for real-time performance

- Advanced CoDense™ technology to reduce program code size

The 64-bit NX45 is an 8-stage superscalar processor that supports RISC-V specification, including “G” (“IMAFD”) standard instructions, “C” 16-bit compression instructions, and “B” bit manipulation, and Andes performance enhancements, plus Andes Custom Extension™ (ACE) for user-defined instructions. It issues two instructions per cycle that significantly increases the performance efficiency that is important for many applications. Its ”B” extensions provide some combination of code size reduction, performance improvement, and energy reduction, and “FD” extensions support IEEE754-compliance single and double precision floating point instructions as well. It incorporates MemBoost to greatly enhance memory bandwidth and reduce memory latencies for applications with intensive memory accesses. In addition, N45 incorporates MemBoost to greatly enhance memory bandwidth and reduce memory latencies for applications with intensive memory accesses. Other features include ECC for memory soft error protection, Platform-Level Interrupt Controller (PLIC) with enhancements for vectored dispatch and priority-based preemption, CoDense™ and StackSafe™ for software quality improvement, PowerBrake and WFI for power management.

Development Tools

- AndeSight™ IDE (Eclipse-based)

- Compiler, Debugger, Profiler, Register Bit-field Display/Update, RTOS Awareness, and more

- Tested platforms: Windows and Linux , single- or multi-user installation

- Andes BSP

- Optimized DSP library

- Demo examples and sample projects

- AndesClarity™: Processor Pipeline Analyzer and Visualizer

- COPILOT: Automation tool for Andes Custom Extension™

- RTOSes

- Open-source: FreeRTOS, Zephyr, RT-Thread

- Commercial: μC/OS-II, ThreadX,

- FPGA Development Boards

- AndeShape™ ADP-XC7 (full-featured)

- Xilinx VCU118

- Debugging Hardware

- AICE-MICRO and AICE-MINI+

Key Features and Performance

AndeStar™ V5 Architecture

| Key Features | Benefits |

|---|---|

| RISC-V RV64GCB ISA |

|

| Andes Custom Extension™ (ACE) option to create custom instructions for software acceleration |

|

| Andes Extended Instructions | Andes exclusive performance and functionality enhancements |

| 16/32-bit mixable instruction format | For compact code density |

| 32 general-purpose registers | For better code size and performance |

CPU Core

| Key Features | Benefits |

|---|---|

| 5.63 Coremark/MHz, 3.27 DMIPS/MHz* | Excellent performance-per-MHz |

| 8-stage dual-issue in-order pipeline | Superior performance-efficiency, while allowing for high speeds |

Extensive branch predication features

|

|

| Physical Memory Protection (PMP), configurable up to 32 regions | Basic read/write/execute memory protection with minimum cost |

| Programmable Physical Memory Attribute (PMA), configurable up to 16 regions | Configurable memory attributes:

|

| Performance monitors | Program code performance tuning |

| StackSafe™ hardware stack protection |

|

Multiplier options

| Option to choose between speed and area according to application's requirements |

| PowerBrake technology | Performance throttling to digitally reduce power consumption |

| QuickNap™ technology | Fast power-down/wake-up support for caches |

* BSP v5.1.0, DMIPS/MHZ follows Dhrystone’s no-inline ground rules, best performances

Memory Subsystems

| Key Features | Benefits |

|---|---|

I-Cache & D-Cache

|

|

ILM & DLM

|

|

| MemBoost | Optimize cache reads and writes to achieve higher bandwidth and lower latency |

| Soft-error protection: parity for I-Cache, and ECC for D-Cache, ILM and DLM | Code and data integrity protection |

| Bus master port: AXI with 64/128/256-bit data, I/D joint or separate bus | User-selectable bus interface for optimal efficiency |

| Bus save port: AXI with 64/128/256-bit data, for ILM/DLM accesses | Efficient data transfer between CPU and SoC masters |

| Core/bus clock ratio of N:1 | Simplified SoC integration |

| 64-bit AXI Peripheral Port Interface | For latecny-sensitve peripheral |

Platform-Level Interrupt Controller (PLIC)

| Key Features | Benefits |

|---|---|

Implements RISC-V PLIC specification

| Allow individual interrupts to be serviced and prioritized without sharing |

Enhanced interrupt features

|

|

Debug Support

| Key Features | Benefits |

|---|---|

| Implements RISC-V debug specifications ver 0.13 | Supported by industry debug tool suppliers |

| JTAG Debug Port | Industry-standard support |

| Embedded Debug Module with up to 8 triggers | Flexible configurations to tradeoff between gate count and debugging capabilities |

| Exception redirection support | Entering debugger upon selected exceptions without using breakpoints |

Trace Support

| Key Features | Benefits |

|---|---|

| Implements RISC-V Trace 1.0 Instruction Trace interface | Supported by Andes tools |

Performance

| Core, Process | NX45, 7nm |

|---|---|

| Frequency (MHz) | 1800 |

| Dynamic power (uW/MHz) | 14.2 |

| Area (mm2) | 0.038 |

* Configured with 32KB instruction and data caches, 16-entry PMP and 16-entry PMA, without DSP and FPU. Using SVT 9-track library, SS corner, 0.81V, -40°C, and with I/O constraint. Power consumption at TT corner, 0.9V, 25°C

Product Package

AndesCore™ NX45 Single-core Processor with AE350 AXI Platform

- Pre-integrated NX45 single-core CPU subsystem, PLIC, Debug Module, and AXI Platform