### **Andes and PUFsecurity Webinar**

24 Feb 2022

### Today's Speakers

• John Min is Director of Field Application Engineering at Andes USA. He has extensive background in Processing – CPU, DSP and ASIC. Prior to Andes, John spent last 20 years in Processor companies like SiFive, MIPS and ARC in various technical roles. Prior to that, he worked in consumer electronics at LG and HP. John has multiple degrees from University of Southern California.

### **Andrew Intro**

• Andrew Irvin, Chairman's office of eMemory and PUFsecurity

15+ years experience across three continents in Sales, Marketing, and Project Management. Originally from the United Kingdom and is a graduate from Edinburgh University. He is also licensed Architect and oversaw the design and construction of serval large building projects in China and Europe prior to moving into the semiconductor industry.

### **Andes Technology Corporation**

#### Who We Are

Pure-play CPU IP Vendor

**RISC-V** Founding **Premier Member**

**Major Open-Source Contributor**/ **Maintainer**

16-year-old **Public** Company

**RISC-V** Ambassador **Running Task Groups Technical Steering Committee Board of Directors**

**Quick Facts**

ANDES

**100**<sup>+</sup>years

**CPU Experience in Silicon Valley**

**20K**<sup>+</sup> 250+ **AndeSight IDE** Licensees installations

Confidential

80+%

Engineers

~10B (Q4/21)

**Total shipment of Andes-Embedded™ SoC**

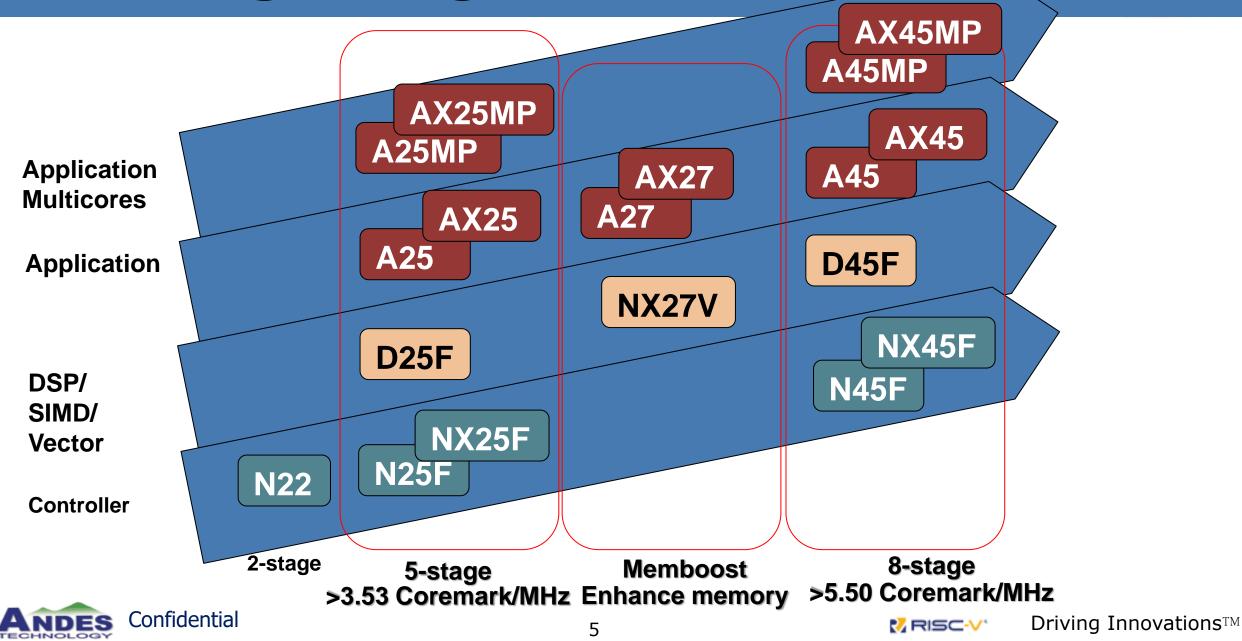

### Large Range of Andes Processors

### **Andes RISC-V Adoption**

#### **<u>Renesas: ASSP MCU</u>** with configurable V5 cores

- Scalable/configurable performance

- Selectable safety feature RENESAS

- Customization options

Feature-rich AndeSight II

RISC-V

Telink: IoT and Wireless Audio with D25F embedded

- Strong integer/DSP performar

- Efficient small data processing

SYSTEMS

Good development tools

Confidential

NDES

#### Picocom: 5G Open RAN small cells

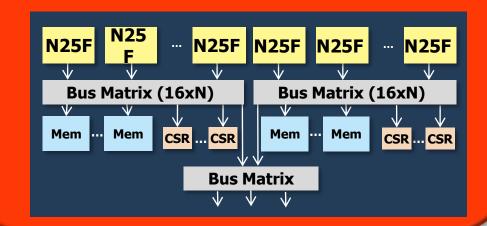

#### AI Accelerators for Servers with >10 NX27V Cores

• RVV with 512-bit VLEN/SIMD

- Custom instructions,

- LLVM compiler

Driving Innovations<sup>TM</sup>

# Securing Andes RISC-V with PUFsecurity

2022 February 24

#### Agenda .

- 1. Company Profile

- 2. Securing the Future of Computing

- 3. The Four Fundamentals of Chip Security

- 4. PUF-based Solutions with Andes RISC-V

PUFsecurity

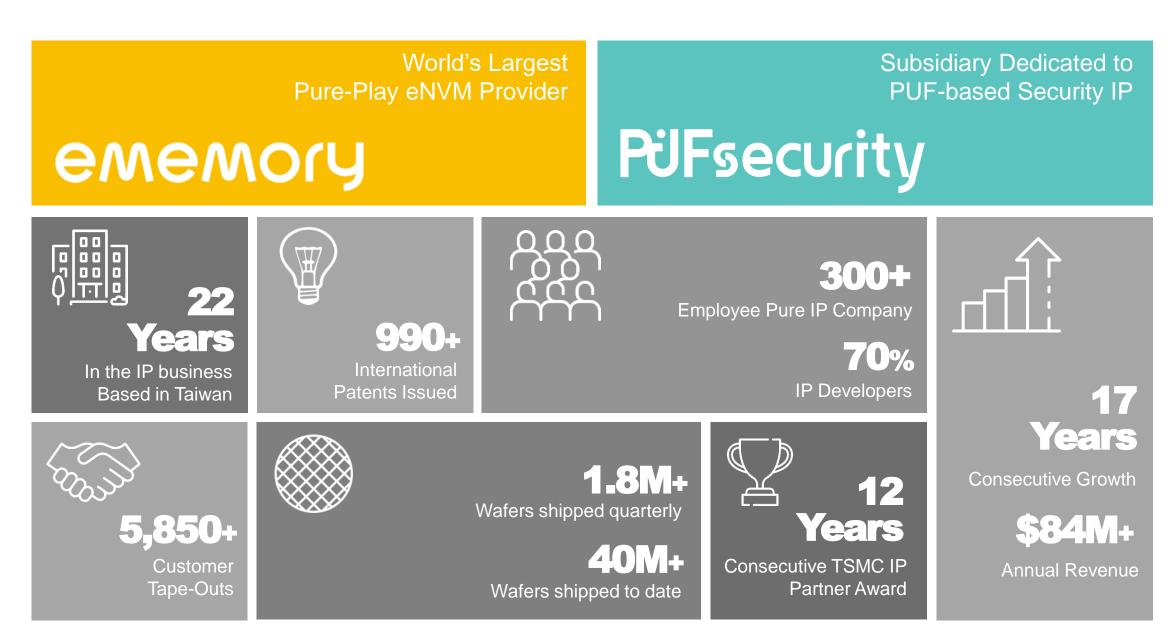

#### Unique Contribution to the Industry -

#### **Logic Non-Volatile Memory**

Provides embedded logic NVM solutions, including both OTP and MTP to Improves yield, performance, and flexibility in product development and production.

#### **Quantum Tunneling PUF**

Provides unique ID for each chip and the necessary hardware 'Root of Trust' to achieve high security solutions whilst also eliminating the need for additional processes.

#### PUF

Physically Unclonable Function

A chip fingerprint for silicon

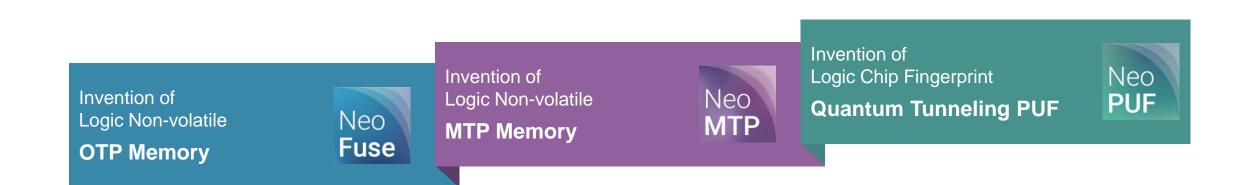

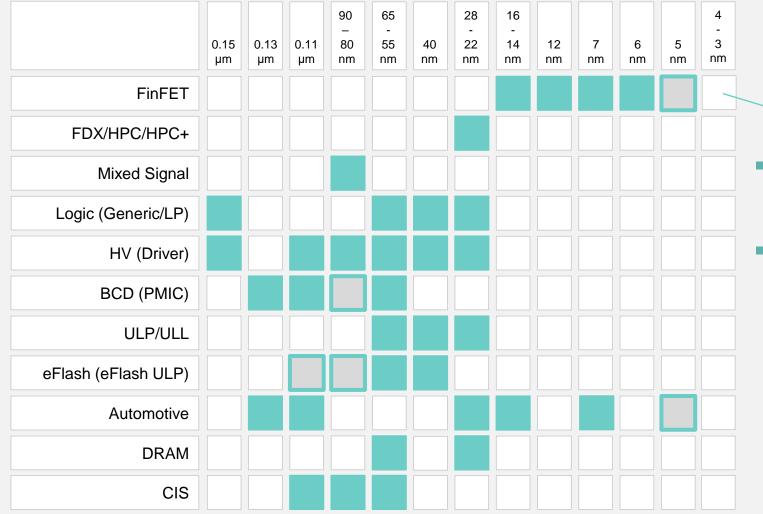

### Widely Available Security IPs .

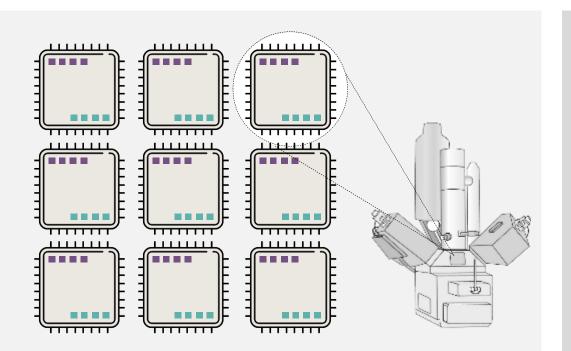

- Qualified/ProductionVerified/DevelopingKickoff in 2022

- NeoPUF adopts the same technology, programming mechanism, and bit cell as NeoFuse

- Qualified NeoFuse stands for NeoPUF and PUF-based IPs readiness

### Hacking is Everywhere

#### Threat to Life

#### Hackers Remotely Kill a Jeep on the Highway

Sparking a 1.4 million vehicle recall by Chrysler, marking the start of the age of hackable vehicles.

Link

Threat to **Privacy**

#### IoT Security Camera hacking demonstration on YouTube

Step by step guides for hacking IoT devices are widely available online.

Link

Threat to Assets

#### Colonial Pipeline pay \$4.4m to end ransomware attack

ending the massive shutdown of approximately half of the USA's East Coast fuel supply

Link

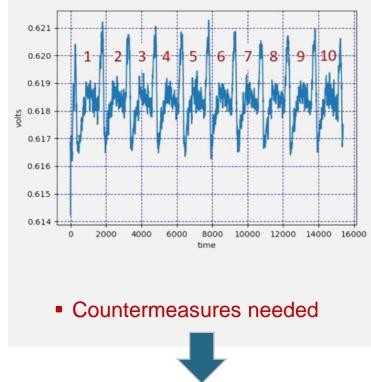

### Hardware Attacks are Today Reality .

M2

Secure Storage needed

**Invisible OTP**

**Fault Injection** Espressif WiFi-IoT Chip Hacked

Differential Power Analysis STM MCU AES key found

Side Channel Attack Protection / Anti-Tampering Design

#### Securing the Future of Computing .

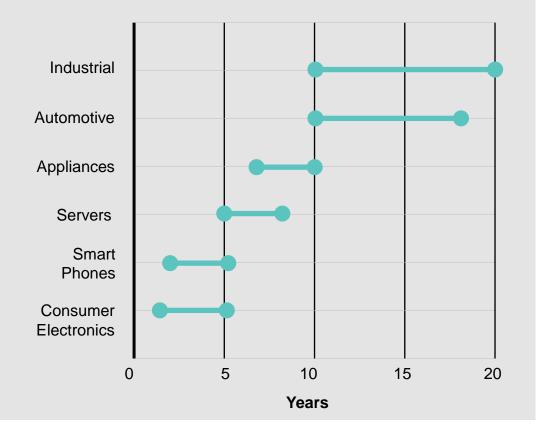

#### **AVERAGE LIFESPAN** (Chip Application by year)

#### The Security Ecosystem's Weakest Link -

#### SECURITY SYSTEM BY COMPUTING LAYER

(and Example Protection Approach)

| Software<br>Application          | https:// for Security                                            | <ul> <li>Software patches can be<br/>applied when being hacked</li> </ul>                           |

|----------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Operating System                 | Isolation                                                        | <ul> <li>Constantly needs upgrades</li> <li>Never know if it is booted</li> </ul>                   |

| Firmware                         | Firmware Encryption                                              | from genuine firmware                                                                               |

| Hardware<br>Cryptographic Engine | Ex. Hardware Crypto Engine,                                      | <ul> <li>Hardware tape-out needed</li> </ul>                                                        |

| Root of Trust                    | Secure BUS and Keys<br>Unknown Key (PUF)<br>Secure Storage (OTP) | <ul> <li>when being hacked</li> <li>Can be Hardware Root of<br/>Trust when well designed</li> </ul> |

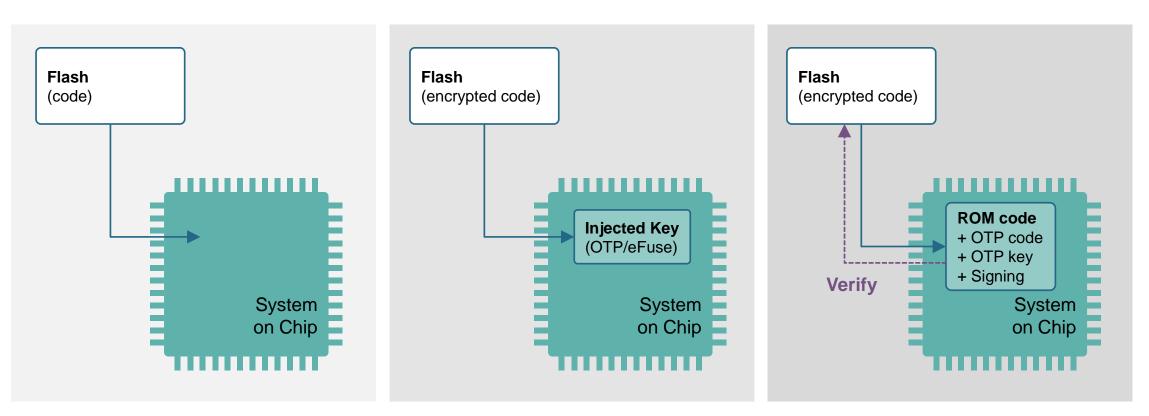

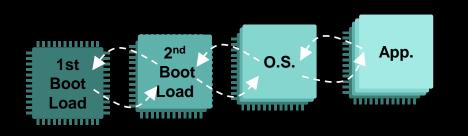

#### How Chips Boot Up is Key to Security -

**3<sup>rd</sup> Generation**

**Secure Booting**

**1st Generation** Conventional Booting

2<sup>nd</sup> Generation

**Improved Booting**

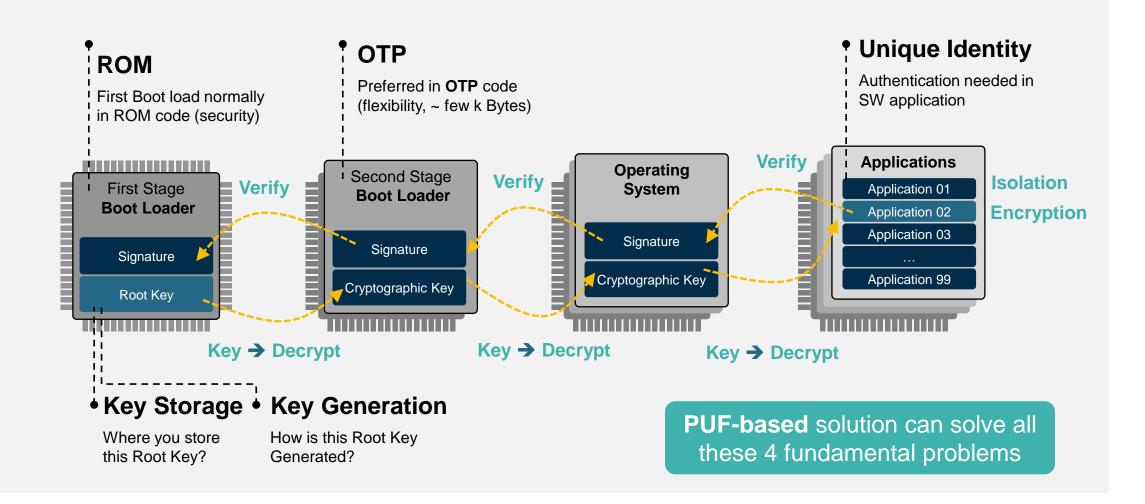

#### Secure Boot Flow (Hardware and Software) -

# The Four Fundamentals of Chip Security

- 1. OTP for Boot Code

- 2. Root Key Storage

- 3. Root Key Generation

- 4. Unique Unclonable Identification

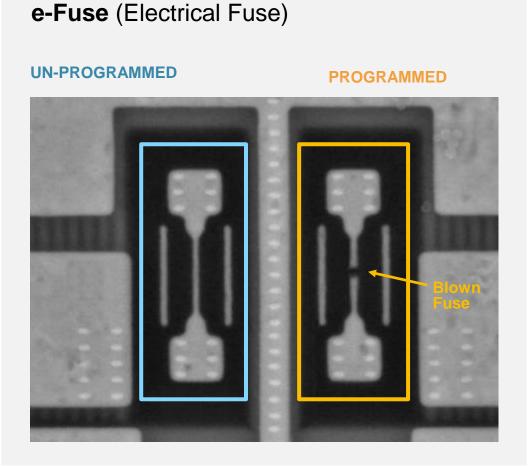

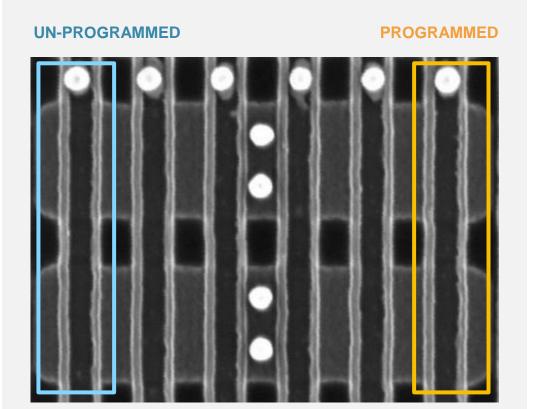

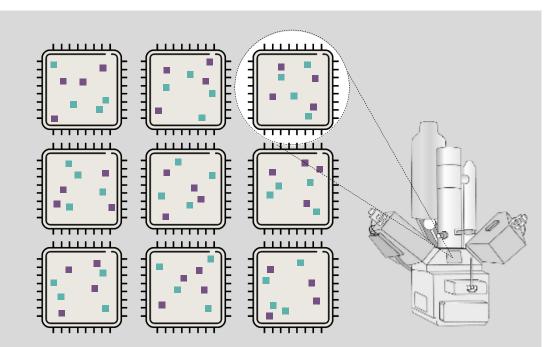

### Physical Invisibility Top View via SEM .

#### anti-Fuse (NeoFuse/NeoPUF)

### Hardware RoT Root Key Storage

#### **eFuse OTP** No PUF-based Storage

OTP address can be easily located

#### Secure OTP With NeoPUF Protection

Different Physical location for each chip

### **Root Key Generation**

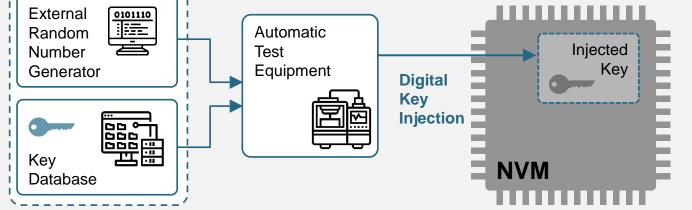

#### **Injected Root Key** (Serial Identification)

#### Initial injection required

- Key Injection must be done during CP/FT

- Secure room (audit) needed

- Extra \$0.5~\$2 per unit cost

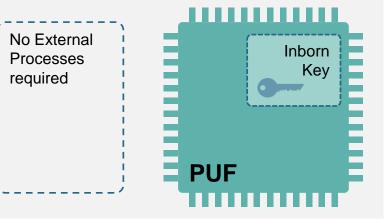

#### Inborn Root Key (PUF-based Identification)

- Inborn, unique, unclonable ID

- Provides zero-touch / zero-trust

- Private key from PUF never exposed outside SOC

### **Combining** Digital and Analog IPs -

| Security Subsystem                  |                                            | Security systems rely on OTP Memory                                                           |

|-------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------|

|                                     |                                            | Secure OTP is replacing eFuse                                                                 |

| Analog Macro<br>(process dependent) | <b>Digital IP</b><br>(process independent) | Crypto engines require TRNG                                                                   |

|                                     |                                            | TRNG is digital + analog                                                                      |

| Anti-Tamper Design                  | Secure CPU                                 |                                                                                               |

|                                     |                                            | External Key injection is expensive                                                           |

| TRNG (entropy)                      | HASH Crypto                                | PUF has zero-touch provisioning                                                               |

| <b>OTP</b> (Secure Storage)         | Symmetric Crypto                           |                                                                                               |

| PUF (Chip Fingerprint)              | Asymmetric Crypto                          | PUF / OTP / TRNG / Anti-tampering combined into one single Hardware Root of Trust IP is Ideal |

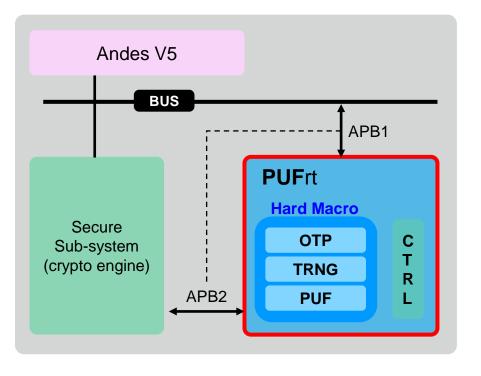

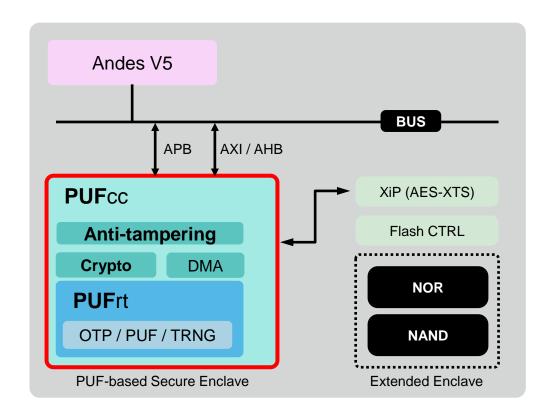

#### PUF-based Security Solutions for RISC-V .

**PUFrt** : Secure Storage (OTP) + Inborn ID / Key (PUF) + Randomness (TRNG) + Anti-Tampering + 3<sup>rd</sup> party security lab certification

**PUFcc** : **PUFrt** + Anti-tampering & NIST-certified Crypto Coprocessor + Secure Enclave (Boundary)

#### **RISC-V Platform Demonstration**

#### **FPGA** Demonstration

by integrating RISC-V (ANDES) and PUFcc (PUFsecurity)

- On-chip Inborn HUK: Saving provisioning cost

- Secure boot using PUFcc: Paired SoC and FW to protect from HW/SW counterfeiting

#### Total Solutions for Hardware Security -

Secure OTP for Key Storage & Boot code

PUF

inborn identity & saving key management flow

TRNG SP800-90B compliant random number

NIST certified Crypto Engines

With encryption and anti-tamper

#### Thank You -

### Andes Advantage

- Standard RISC-V ISA with Andes Extensions

- AndeStar V5 ISA Extensions to accelerate and secure computing

- StackSafe<sup>TM</sup>: HW supported stack protection

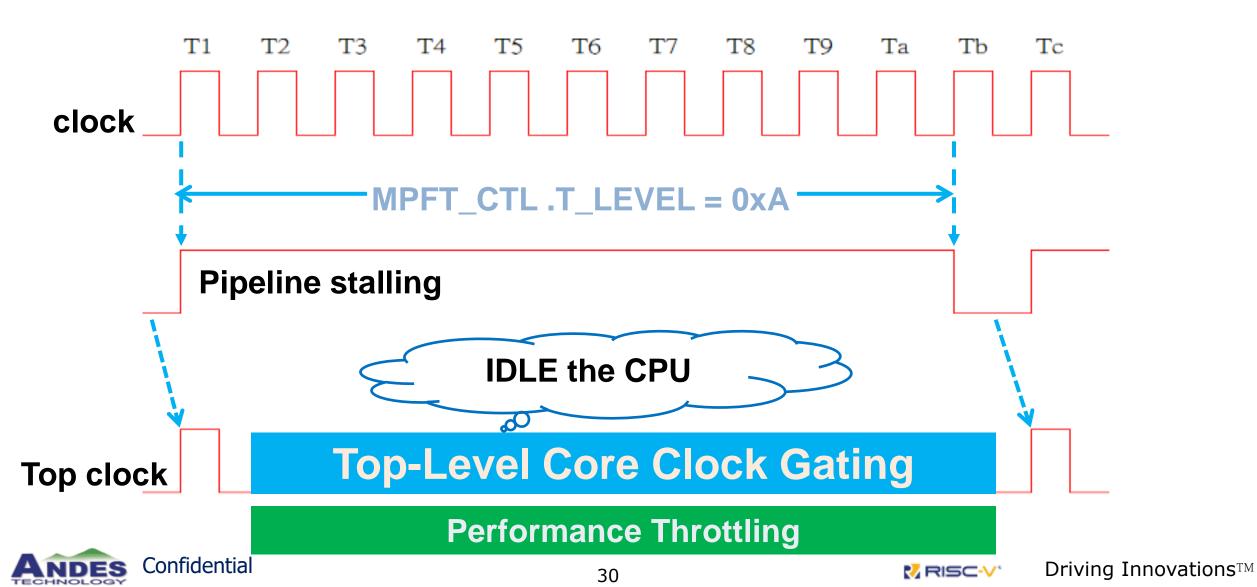

- **PowerBrake** : Stalling pipeline to save powe

- **QuickNap**<sup>TM</sup> : Fast power-down/wake-up support for caches

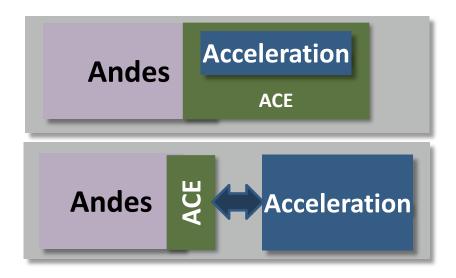

- ACE Andes Custom Extensions

- Custom Instructions Accelerate Instruction

- Custom Memories Fast and local operands

- Custom Ports Accelerate, move, and secure predictable bus

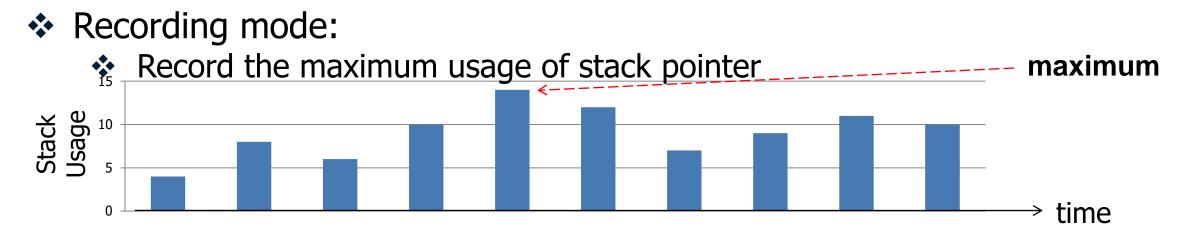

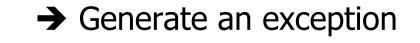

### StackSafe<sup>TM</sup>: Protect Stack Usage

#### Protection mode:

- Allocate stack size and set its bound accordingly

- When stack pointer grows over the bound

**Exception**!

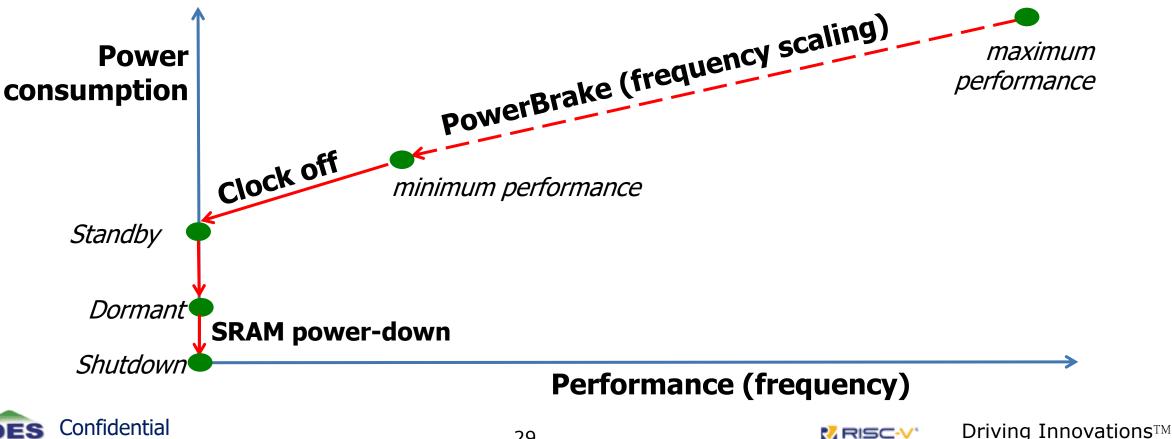

### **PowerBrake & QuickNap<sup>TM</sup>: Power Management**

PowerBrake to digitally adjust power (via stalling pipeline) ◆ QuickNap<sup>TM</sup>: logic power-down and SRAM in retention

- Put dirty bits in tag SRAM instead of flops

- Eliminate the need to flush data cache

### **PowerBrake**

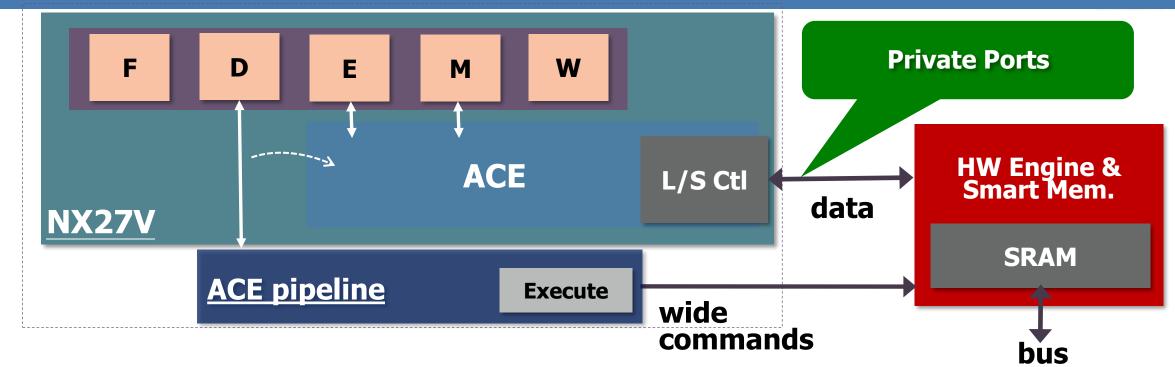

### ACE Andes Custom Extensions

#### **ACE for Performance and Security**

- RISC-V ISA extension enables

- New instructions

- New coprocessors

- New memory locations

- Andes eases extension with

- ACE key words in System C framework

- Rich semantics for new instructions

- Fully automated COPILOT generator

- Integrating acceleration & RISC-V core

- Resource & data hazard protection

- Simulator, compiler, assembler, etc.

- Test vectors for verification

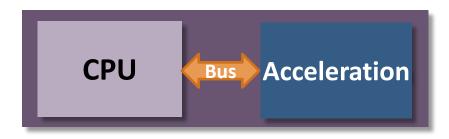

#### **Vs Traditional Architecture.**

### **Private Port for Data Isolation**

- ✤ A usage example

- HW engine: application-specific DMA and structured computations (e.g. CNN)

- ACE instructions: control HW engine, and load/store data to/from VRF

- Advantages:

- HW engine is tightly-coupled

- Data accesses are more efficient

- Data accesses are isolated

# Q&A

## Thank you!