#### Agenda

- Andes and RISC-V

- Virtual Prototyping

- AndeSysC™

- Virtual SoC Example

### Andes and RISC-V

#### Who We Are

Pure-play CPU IP Vendor

RISC-V Founding Premier Member

Major Open-Source Contributor/Maintainer

16-year-old Public Company

RISC-V Ambassador Running Task Groups TSC Vice Chair Director of the Board

USA o

#### **Quick Facts**

**100**<sup>+</sup> years

80%

CPU Experience in Silicon Valley

R&D

200+

**20K**

**7B**+

Licensees

AndeSight IDE installations

Total shipment of Andes-Embedded™ SoC

Taking RISC-V® Mainstream

TW (HQ)

### Successful Stories with Andes

# Renesas: ASSP MCU with configurable V5 cores

- Scalable/configurable performance

- Selectable safety features

- Customization options

- Feature-rich AndeSight IDE

# Telink: IoT and Wireless Audio with D25F embedded

- Strong integer/DSP performance

- Efficient small data processing

- Good development tools

#### Picocom: 5G Open RAN small cells

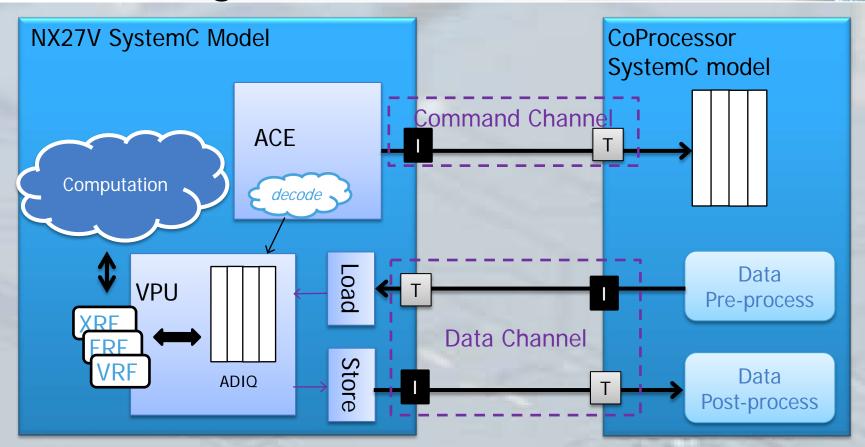

# Al Accelerators for Servers with >10 NX27V Cores

- RVV with 512-bit VLEN/SIMD

- Custom instructions

- LLVM compiler

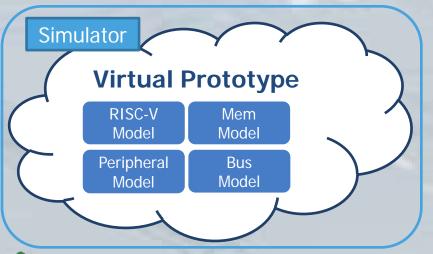

# Virtual Prototyping

- A method in the process of product development

- Using software to validate a design before committing to making a physical prototype

- Behavior, function and cycle analysis

#### Equivalent

- Behavior

- Function

- Cycle

# Benefit of Virtual Prototyping

### Enable parallel development of hardware and software

- Enable earlier feedback between HW and SW teams

- Support co-verification of hardware and software

- Make chip re-spins much less likely

- Reduce project time and cost

Time

# Electronics System Level (ESL)

- Defined by Gartner Dataquest in 2001

- Methodologies for HW/SW Co-design and Co-verification

- Higher level abstraction above RTL

- C, C++

- SystemC/TLM2.0 (IEEE 1666 -2011)

- UPF 3.0 (IEEE 1801-2015)

- IP-XACT (IEEE 1685 -2014)

- and more

"the utilization of appropriate abstractions in order to increase comprehension about a system, and to enhance the probability of a successful implementation of functionality in a cost-effective manner."

-- ESL Design and Verification: A Prescription for Electronic System Level Methodology July 27, 2010

### SystemC and TLM2.0

- SystemC is defined and promoted by Open SystemC Initiative (Accellera)

- A system level modeling language which provides event-driven simulation interfaces

- Set of C++ classes and macros

- Modules, Ports, Signals, Processes, Channels etc...

Calculate and represent all the operations, state changes, data movements and computations

SYSTEMC

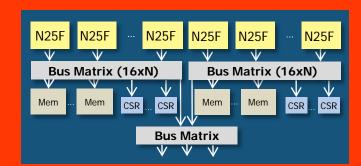

# AndeSysC™

- Andes virtual platform solution based on SystemC

- Near-cycle accurate, extensible and flexible models of AndesCore™ V5 RISC-V processor IP's

- AndeShape™ platform IP components

- Andes Custom Extension™ (custom instructions)

- AndeSight™ IDE and AndeSoft™ SW stack

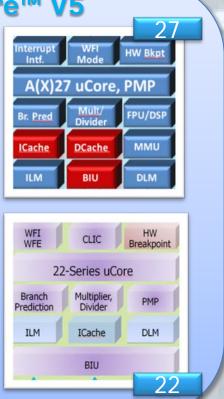

### Supported AndesCore™ Features

#### CPU IPs

- AndesCore™ RISC-V V5 Cores

- All 22-/25-/27-/45-series

#### Architecture features

- Interruption Architecture (PLIC)

- Performance Monitoring

- Hardware Stack Protection

- Control and Status Registers

- Optional:

- MMU/MPU

- Icache and Dcache

- Floating Point Unit

- Digital Signal Process Unit

• ...

25

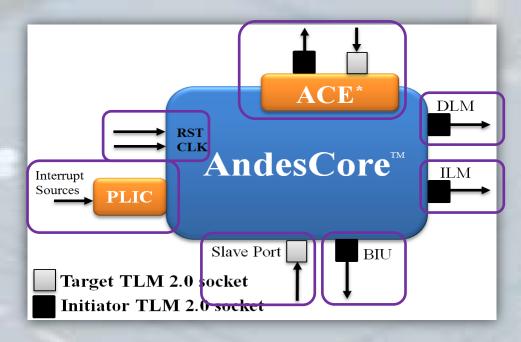

# Supported Interfaces

- Clock and Reset Pin

- DLM Port

- ILM Port

- Interrupt Pins

- Slave Port

- Bus Interface Unit

- ACE Interfaces (e.g. ACM and ACP)

### Supported Platform IPs

- DMA Controller (DMAC)

- GPIO

- LCD Controller (LCDC)

- Real Time Clock (RTC)

- Secure Digital Host Controller (SDC)

- Synchronous Serial Port (SSP)

- Timer

- UART Controller

- Watchdog Timer (WDT)

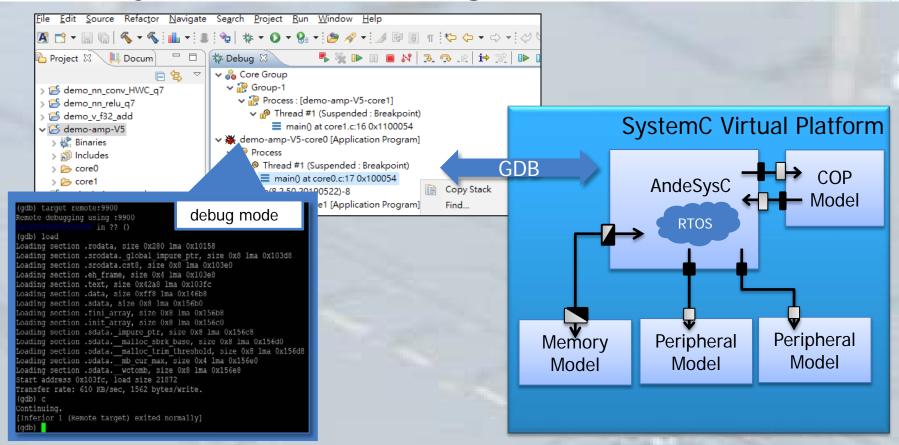

### Streaming Port

# Execute AndeSysC of Streaming Port

#### 1.Executing SystemC simulator

```

SystemC 2.3.3-Accellera --- Mar 8 2021 10:57:53

Copyright (c) 1996-2018 by all Contributors,

ALL RIGHTS RESERVED

AndeSystemC v1.1.182.495 (d71f87c)(ndsv5core.cxx)

AndeSystemC v1.1.182.495 (d71f87c) (v5 wrapper.cxx)

AndeSystemC v1.1.182.495 (d71f87c) (v5 pseudo bus.cxx)

AndeSystemC v1.1.182.495 (d71f87c) (v5 pseudo bus.cxx)

AndeSystemC v1.1.182.495 (d71f87c) (nds tlm2 adapter.cxx)

AndeSystemC v1.1.182.495 (d71f87c) (v5 tlm2 idlm slave.cxx)

AndeSystemC v1.1.182.495 (d71f87c) (v5 tlm2 idlm slave.cxx)

socketiobase: using fd 4

socketiobase: server at :::9900

GDB init ...

OB init skipped

ig NX27V (9900)

```

#### 2. Running Design dled.

```

Type 3 instruction is decoded.

CP: 181304 ns

Type 3 instruction is handled.

Type 3 instruction is decoded.

Type 3 instruction is decoded.

Type 2 instruction is decoded.

Type 2 instruction is decoded.

CP: 189504 ns

Type 3 instruction is handled.

CP: 197704 ns

Type 3 instruction is handled.

CP: 205904 ns

Type 3 instruction is handled

```

#### 3. Execution Finished

```

ISS FINISHED ----

Config NX27V total icount

: 00011821

Config NX27V total cycle

: 00109963

Config NX27V stall cycle

: 00098142

Config NX27V icache access : 00000000

Config NX27V icache miss

: 00000000

Config NX27V dcache access: 00000000

Config NX27V dcache miss

: 00000000

Config NX27V Branches Num

: 00003822

Config NX27V BTB mispred

: 00000103

socketio: ieof1

GDB init skipped

[AndeSysC] Simulation Finished

```

o: /OSCI/SystemC: Simulation stopped by use

### AndeSysC and AndeSight

### AndeSysC™ Summary

### Compatibilities with Flexibility

- Supported by AndesCore<sup>™</sup> and AndeShape<sup>™</sup> Platform models

- Compatible with 3<sup>rd</sup> parties' IP's/tools using TLM2.0 protocol

- Flexibility to configure and construct any virtual SoC

### Near-Cycle Accurate Simulation

- Early profiling during the rapid prototyping stage

- High level estimation of performance for the eventual real devices

### Development Acceleration

- Interact directly w/ feature-rich AndeSight™ and AndeSoft™

- Facilitate HW/SW Co-design through virtual prototyping