Simon TC Wang Technical Marketing Manager Andes Technology April 26, 2021

- AndeSight™ IDE

- AndeSoft<sup>™</sup> BSP

- AI Software Stack

- DSP and Vector programming

- NN library and real NN model use cases

### **Andes at A Glance**

#### Who We Are

Pure-play **CPU IP Company**

**RISC-V Founding** Premier Member

Taiwan Stock **Exchange Listed**

Major Open-Source Contributor/Maintainer

Director of the Board Vice Chair of TSC **Running Task Groups RISC-V Ambassador**

years old company 80% R&D employees

**7B**<sup>+</sup>(By end of 2020) accumulated Andesembedded SoC shipped

200<sup>+</sup> Licensees Worldwide 20K+ AndeSight IDE installation

Taking RISC-V® Mainstream

# AndeSight™ IDE

Comprehensive Development Environment

### **AndeSight™ IDE for RISC-V**

Accelerate your RISC-V software developments with the comprehensive development environment!

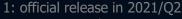

### **AndeSight™ IDE**

with AndeSoft™ BSP inside

- User-friendly and easy-to-use IDE

- Highly-optimized GCC/LLVM toolchains for outstanding performance and compact memory footprint

- Abundant demos for boosting your development

- Rich RTOSes and Linux (LTP verified)

- Optimized compute library: DSP, Vector<sup>1</sup>

- Peripheral drivers for AndeShape™ platform

- Near cycle-accurate simulators: AndeSim™

- Arduino support for Andes Corvette EVB

### **SoC SW Development Environment**

## The state of the s

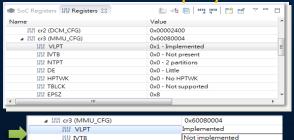

### **AndeSight™: Professional IDE**

### ■ Eclipse-based IDE, enriched from 16-year continuous development

#### Bit-filed display

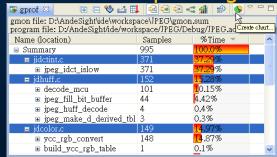

#### **Function profiling**

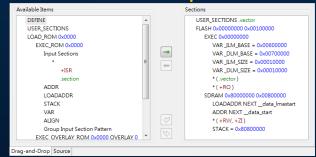

#### Meta linker script editor

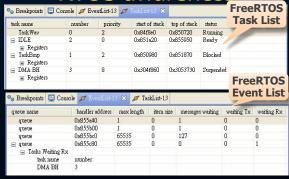

#### **RTOS** awareness

1919 NTPT

#### Custom plugin

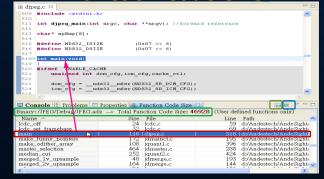

#### Function code size

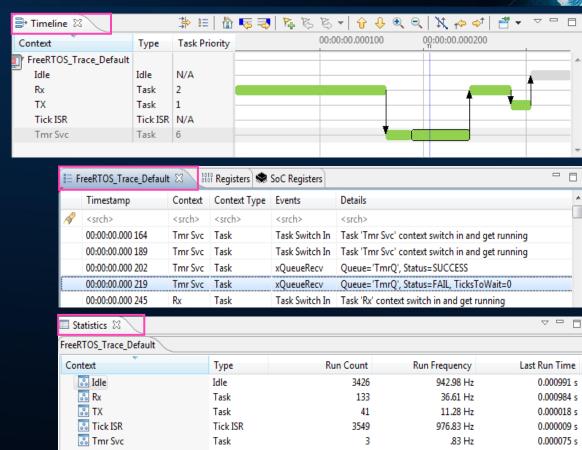

### **FreeRTOS Timeline Analyzer**

■ Visualize the runtime execution behaviors of task, interrupts and events within a period of time¹

1: EVB target only

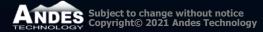

### **Multicore Development Support**

Build and debug the multicore software with separate configurations by simply creating multicore projects

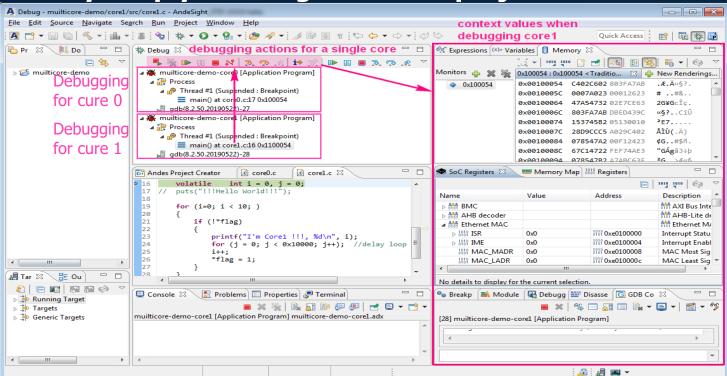

### **Core Grouping**

- **Grouping Cores for Efficient Debugging**

- Debug commands can be sent to a specific set of cores at the same time.

### **AndeSight™ Scripting**

- **Record and replay UI operations with Python script**

- Test automation

- Issue reproduction

Search Navigate Project Run Window Help ☆ Debug

□ P X B demo\_nn\_conv\_HWC\_ < < terminated > demo\_nn\_relu\_q7 Default [Application Program] ✓

✓ demo\_nn\_relu\_q7 demo\_nn\_relu\_q7 Default<terminated, exit value: 0>gdb(8.2.50.2) Build Targets > Binaries > m Includes > 🗁 bin > > Default Script Shell ⋈ script testing. demo nn relu q7.le project.select('sc') Start to record U run.py project.select('demo nn relu q7') run.py.log run('demo nn relu q7 Default') operations > 15 demo v f32 add run.select('demo nn relu q7 Default') run.select('demo nn relu q7 Default') rvv-intrinsics-examples run.config('run.py').create('Script') run('run.py') run('demo nn relu q7 Default') run.select('demo nn relu q7 Default')

Python script

## AndeSoft™ BSP

Application Building Blocks Inside of AndeSight™ IDE

### AndeSoft™ BSP: Application Building Blocks

#### **Fundamental**

- Compiler/Toolchain are contributed to and supported officially by **GNU/LLVM** communities

- Optimized **MCUlib**, newlib and glibc

- Optimized low-level compute libraries for NN, DSP and vector processing: **libnn**, **libdsp**, **libvec**

- Fast and near cycle-accurate simulators: AndeSim<sup>™</sup>, AndeSysC<sup>™</sup>, Qemu<sup>1</sup>

- Debugging: GDB and ICEman (speed-optimized OpenOCD)

- Concise linker script and its tools, Linker Scattering-and-Gathering (LdSaG)

- Bare-metal drivers and demo programs to demo AndesCore™ features

#### **Real-Time Operating Systems**

#### **Linux, Middleware and SW Framework**

- Linux kernel v4.17 and LTS v5.4, device drivers and advanced features: strace, ftrace, Perf, SMU, power throttling, suspend to RAM, HIGHMEM and kernel module

- U-Boot, OpenSBI and BBL

### **AndeSoft**<sup>TM</sup>: Bare Metal

■ Rich startup demo projects for Andes-specific features

| Categories       | Startup demo                                                 |

|------------------|--------------------------------------------------------------|

| Interrupt        | PLIC, CLIC                                                   |

| Memory           | MMU, PMP, PMA, cache, cache lock, ECC, bus matrix slave port |

| Power Management | PowerBrake, hibernate, WFI CPU standby/resume                |

| Programming      | DSP, printf UART redirect, C++ programming                   |

| Misc             | StackSafe™, performance monitor, SMP                         |

- AMSI (Andes MCU Software Interface) driver APIs

- DMA, Flash, GPIO, I2C, PWM, RTC, SPI, UART and WDT

### AndeSoft<sup>TM</sup>: Linux

#### **■ Linux kernel**

- Mainline Linux compatible

- V4.17 and LTS v5.4, RV[32|64]GC, SMP

- Cache coherence and non-coherence support

- Linux Test Projects (LTP) verified

- Device drivers for AndeShape™ AE350 platform

#### **■** Kernel features

- strace/ftrace to debug Linux applications easily

- Perf to evaluate the system bottleneck

- Power Management

- Suspend-to-RAM: suspended by sysfs and wakeup by RTC and UART interrupt

- PowerBrake: power throttling controlled by sysfs

- **Kernel module** all RV32/RV64 relocation type

- HIGHMEM support >1GB memory for RV32

- CPU hotplug

#### ■ U-Boot, U-Boot-spl, OpenSBI and BBL

### AndeSoft<sup>TM</sup>: Linux

**Linux Distribution and Build System**\*

\*: available upon request

- **Andes GitLab Service for Linux Development Packages**

- A public web service: git.andestech.com

- Under Andes Maintenance Program

## **AI Software Stack**

**DSP, Vector and NN Programming**

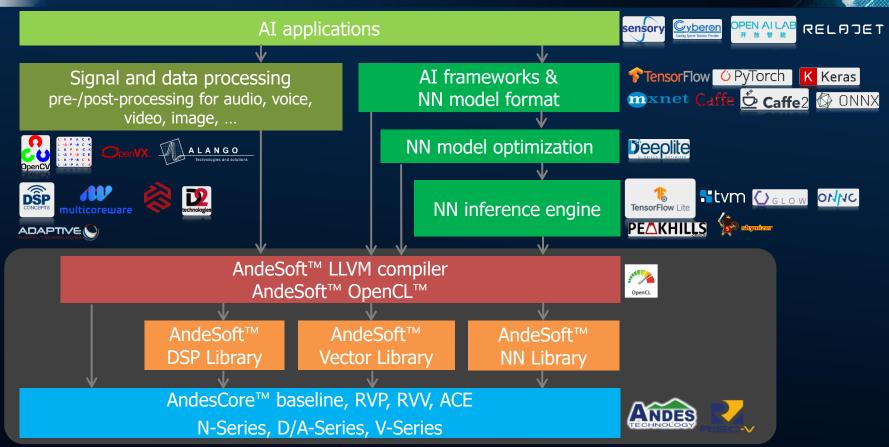

### **AI Software Stack and Ecosystem**

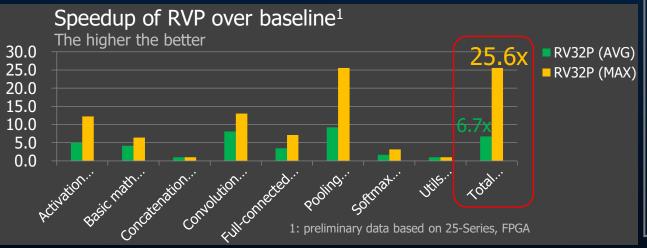

### First implementation of RISC-V DSP/SIMD extension (RVP)

- DSP intrinsic functions: as C-like functions without writing error-prone assembly

- AndeSoft™ DSP library: ~300 functions in 10 categories

- ➤ Basic, complex, controller, distance, filtering, matrix, statistic, SVM, transform, utils

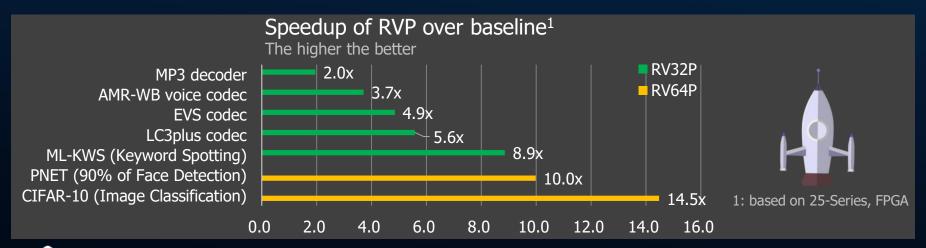

- Increase power efficiency to your DSP applications: 2.0x-5.6x speedup for codecs, and 8.9x-14.5x speedup for NN models

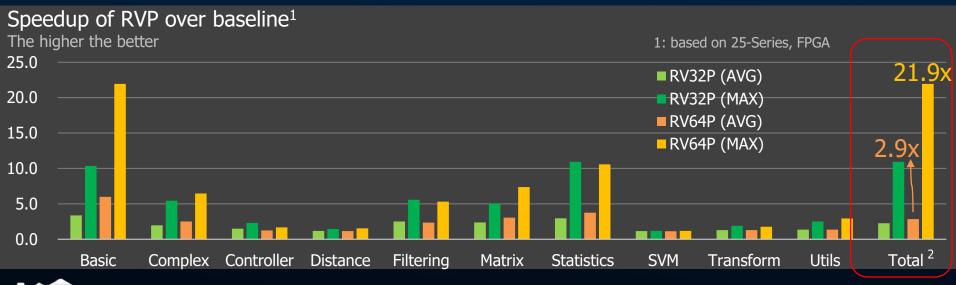

### **AndeSoft™ DSP Library**

- Optimized low-level DSP functions for RISC-V Baseline and RVP processors

- Compatible with CMSIS-DSP API

- Compiler automatically generates partial RVP instructions to facilitate development

- Boost signal processing performance

- Speedup 2.9x in average and 21.9x in maximum

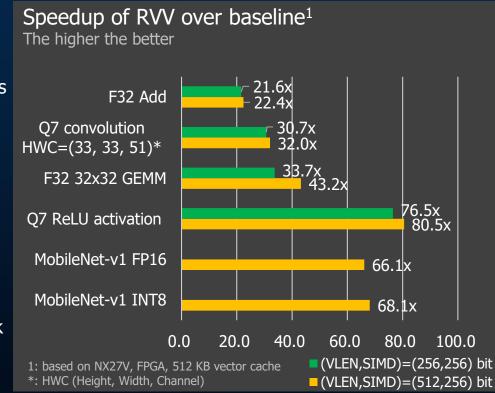

### **RISC-V Vector Software Solutions**

## ■ Standard software solutions in AndeSight™ IDE

- AndeSim™: new cycle-accurate simulator

- Toolchains: intrinsic functions, as C-like functions without writing error-prone assembly

- AndeSoft™ Vector library:

- Optimized for RISC-V baseline and RVV processors

- > 100 functions in 5 categories: basic, filtering, image, matrix, and transform

- Compatible with NE10 library APIs

#### ■ Advanced software solutions

- AndeSysC™: SystemC support for AndeSim™

- AndesClarity™: GUI-based processor pipeline visualizer and analyzer

- AndeSoft™ NN library: optimized neural network functions

## Anors -

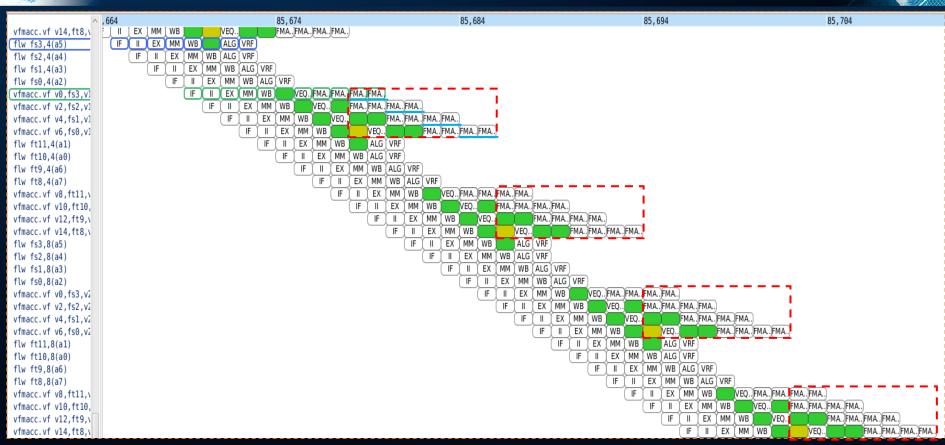

### AndesClarity™ Processor Pipeline Analyzer

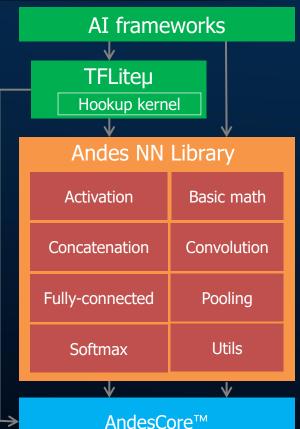

### **AndeSoft™ NN Library**

- Optimized neural network functions for Pure-C, RVP, and RVV processors

- Boost NN performance by using SIMD and vector instructions

- >120 functions in 8 categories

- Compatible with CMSIS-NN APIs

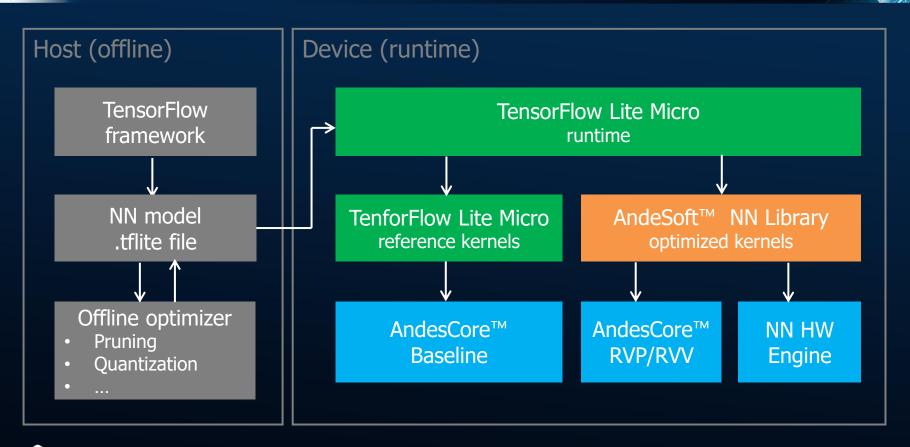

### **Inference Flow with TensorFlow Lite Micro**

| Categories      | Operators             | NN Library API <sup>1</sup>                                                                             |  |  |

|-----------------|-----------------------|---------------------------------------------------------------------------------------------------------|--|--|

|                 | Sigmoid<br>Tanh       | riscv_nn_activate_[q7 q15]                                                                              |  |  |

|                 |                       | riscv_nn_relu_[q7 q15]<br>riscv_nn_leaky_relu_q7                                                        |  |  |

| Basic           | FIRMENT-WISE          | riscv_nn_ew_add_s8 riscv_nn_ew_mul_s8                                                                   |  |  |

| Concatenation   | Concatenation         | riscv_nn_concate_s8_[w x y z]                                                                           |  |  |

| Convolution     | Pointwise convolution | riscv_nn_conv_HWC_[q7 u8 s8 q15]<br>riscv_nn_conv_1x1_HWC_[q7 u8 s8]<br>riscv_nn_conv_dw_HWC_[q7 u8 s8] |  |  |

| Fully-connected | Fully-connected       | riscv_nn_fc_[q7 u8 s8 q15]                                                                              |  |  |

| PAAIINA         |                       | riscv_nn_maxpool_[q7 s8]_HWC<br>riscv_nn_avepool_[q7 s8]_HWC                                            |  |  |

| Softmax         | Softmax               | riscv_nn_softmax_[q7 u8 s8 q15]                                                                         |  |  |

| Utils           | Reshape               | riscv_nn_reshape_s8                                                                                     |  |  |

1: including but not limited to the list

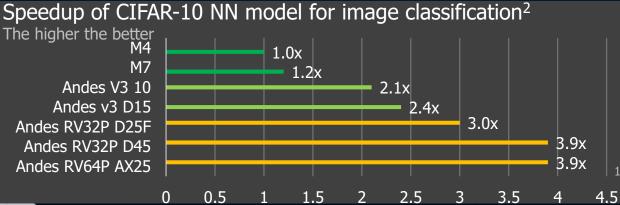

### **Use Case: CIFAR-10 NN Model**

| CIFAR-10   | Operators                        | NN Library APIs                                   |

|------------|----------------------------------|---------------------------------------------------|

| llaver i   |                                  | riscv_nn_conv_HWC_q7_RGB_fast<br>riscv_nn_relu_q7 |

|            | Pooling (maxpool)                | riscv_nn_maxpool_q7_HWC                           |

| II 2V/Or / |                                  | riscv_nn_conv_HWC_q7_fast<br>riscv_nn_relu_q7     |

|            | Pooling (maxpool)                | riscv_nn_maxpool_q7_HWC                           |

| llaver 3   | Convolution<br>Activation (ReLU) | riscv_nn_conv_HWC_q7_fast<br>riscv_nn_relu_q7     |

|            | Pooling (maxpool)                | riscv_nn_maxpool_q7_HWC                           |

| layer 4    | Fully-connected                  | riscv_nn_fc_q7_fast                               |

| layer 5    | Softmax                          | riscv_nn_softmax_q7                               |

- ✓ Performance boost with AndeSoft™ NN library

- Increase power efficiency

- ✓ Lower response time

1: based on 25-Series, FPGA

### **Use Case: MobileNet-v1 NN Model**

#### Inference latency of MobileNet-v1 NN model for object detection

The lower the better

| MobileNet-v1                        | Data | ISA  | VLEN  | SIMD  | Real chip latency      | Nomalized latency <sup>3</sup> |

|-------------------------------------|------|------|-------|-------|------------------------|--------------------------------|

| MODITEMET-VI                        | Туре | ISA  | (bit) | (bit) | (ms)                   | (ms @1GHz, 1 core)             |

| CA9 (Xilinx PYNQ) <sup>1</sup>      |      | NEON |       | 128   | 721.4 @650MHz, 2 cores | 703.4                          |

| CA53 (Raspberry Pi-3B) <sup>1</sup> | FP32 | NEON |       | 128   | 121.8 @1.2GHz, 4 cores | 438.5                          |

| CA72 (Firefly RK3399) <sup>1</sup>  | rr32 | NEON |       | 128   | 77.9 @1.8Hz, 2 cores   | 210.3                          |

| CA73 (Kirin 970) <sup>1</sup>       |      | NEON |       | 128   | 41.3 @2.36GHz, 4 cores | 292.4                          |

| Andes NX27V <sup>2</sup>            | FP16 | RVV  | 512   | 256   |                        | 62.3                           |

| Andes A27L2 <sup>2</sup>            |      | RVP  |       | 32    |                        | 564.5                          |

| Andes AX27L2 <sup>2</sup>           | INT8 | RVP  |       | 64    |                        | 358.5                          |

| 1: TVM | , https://git | thub.com/ar | ache/tvm/v | wiki/Benchmark | #arm-cpu |

|--------|---------------|-------------|------------|----------------|----------|

|--------|---------------|-------------|------------|----------------|----------|

<sup>2:</sup> AndeSoft™ NN Library, PyTorchCV imagenet-1k "MobileNet x1.0", https://pypi.org/project/pytorchcv/ preliminary data based on FPGA and scaling to 1.0 GHz. Real SoC performance will depend on memory subsystem

| Type / Stride | 1. MobileNet Body Archi<br>Filter Shape | Input Size                 |

|---------------|-----------------------------------------|----------------------------|

| Conv/s2       | $3 \times 3 \times 3 \times 32$         | $224 \times 224 \times 3$  |

| Conv dw / s1  | $3 \times 3 \times 32 \text{ dw}$       | $112 \times 112 \times 32$ |

| Conv/s1       | $1 \times 1 \times 32 \times 64$        | $112 \times 112 \times 32$ |

| Conv dw / s2  | $3 \times 3 \times 64 \mathrm{dw}$      | $112 \times 112 \times 64$ |

| Conv/s1       | $1 \times 1 \times 64 \times 128$       | $56 \times 56 \times 64$   |

| Conv dw / s1  | $3 \times 3 \times 128 \mathrm{dw}$     | $56 \times 56 \times 128$  |

| Conv/s1       | $1 \times 1 \times 128 \times 128$      | $56 \times 56 \times 128$  |

| Conv dw / s2  | $3 \times 3 \times 128 \mathrm{dw}$     | $56 \times 56 \times 128$  |

| Conv/s1       | $1 \times 1 \times 128 \times 256$      | $28 \times 28 \times 128$  |

| Conv dw / s1  | $3 \times 3 \times 256 \mathrm{dw}$     | $28 \times 28 \times 256$  |

| Conv/s1       | $1 \times 1 \times 256 \times 256$      | $28 \times 28 \times 256$  |

| Conv dw / s2  | $3 \times 3 \times 256 \mathrm{dw}$     | $28 \times 28 \times 256$  |

| Conv/s1       | $1 \times 1 \times 256 \times 512$      | $14 \times 14 \times 256$  |

| 5× Conv dw/s1 | $3 \times 3 \times 512 \mathrm{dw}$     | $14 \times 14 \times 512$  |

| Conv/s1       | $1 \times 1 \times 512 \times 512$      | $14 \times 14 \times 512$  |

| Conv dw / s2  | $3 \times 3 \times 512 \mathrm{dw}$     | $14 \times 14 \times 512$  |

| Conv/s1       | $1 \times 1 \times 512 \times 1024$     | $7 \times 7 \times 512$    |

| Conv dw / s2  | $3 \times 3 \times 1024 \text{ dw}$     | $7 \times 7 \times 1024$   |

| Conv/s1       | $1 \times 1 \times 1024 \times 1024$    | $7 \times 7 \times 1024$   |

| Avg Pool/s1   | Pool 7 × 7                              | $7 \times 7 \times 1024$   |

| FC/s1         | $1024 \times 1000$                      | $1 \times 1 \times 1024$   |

| Softmax / s1  | Classifier                              | $1 \times 1 \times 1000$   |

| T-1-1- | 2 | D        | D   | T   |     | The | _ |

|--------|---|----------|-----|-----|-----|-----|---|

| able   | L | Resource | Per | Lav | /er | IV  |   |

|        |   |          |     |     |     |     |   |

| Туре            | Mult-Adds | Parameters |

|-----------------|-----------|------------|

| Conv 1 × 1      | 94.86%    | 74.59%     |

| Conv DW 3 × 3   | 3.06%     | 1.06%      |

| Conv 3 × 3      | 1.19%     | 0.02%      |

| Fully Connected | 0.18%     | 24.33% 知乎  |

<sup>3:</sup> Scale to the same frequency; estimated performance 4 cores="3"\*1 core, the magic number "3" is from experience

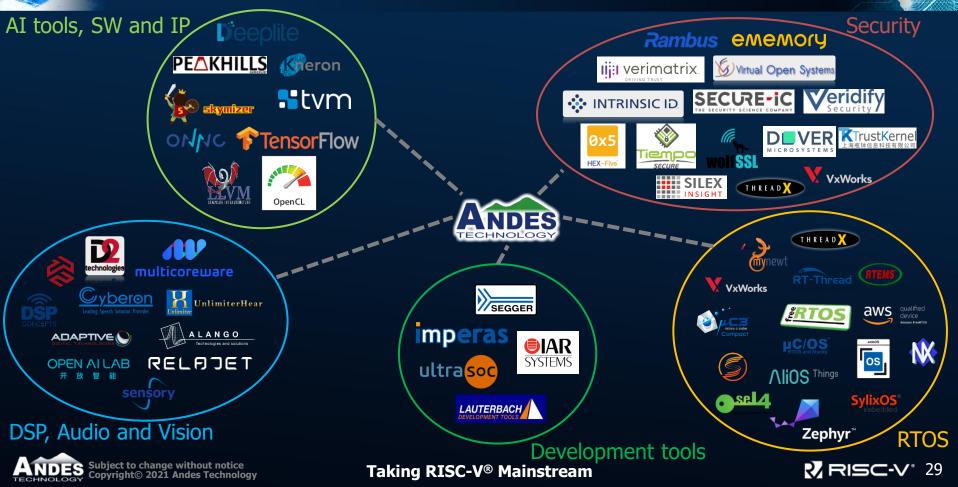

# **Andes Ecosystem**

### **Andes Partners and Ecosystem**

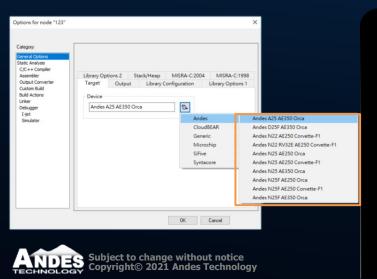

- Complete build and debug toolchain for RISC-V

- Support all series of Andes RISC-V CPU¹

- Functional Safety Certified

- IEC 61508

- ISO 26262

- EN 50128

- IEC 62304

Toolchain

Compiler

C-STAT

Functional

Safety

- 1: AndesCore<sup>™</sup> 45-Series will be available in the mid-year of 2021

- 2: Part of Andes V5 RISC-V extensions are supported in the mid-year of 2021

### **AWS Device Qualification Program for FreeRTOS**

- AndeShape<sup>™</sup> Corvette-F1 N25 now is an AWS FreeRTOS-qualified evaluation platform

- The FreeRTOS port is verified and executes smoothly and consistently with AWS IoT

- FreeRTOS kernel, Wi-Fi management, TCP/IP stack, PKCS#11<sup>1</sup>, TLS<sup>2</sup>, MQTT<sup>3</sup>

<sup>2:</sup> Transport Layer Security

<sup>3:</sup> Message Queue Telemetry Transport

### Summary

### ■ AndeSight<sup>™</sup> IDE

- User-friendly and easy-to-use IDE

- Accelerate your RISC-V software developments with the comprehensive development environment

#### ■ AndeSoft<sup>™</sup> BSP

- Highly-optimized toolchains for better performance and smaller memory footprint

- Well-integrated building blocks to reduce time-to-market

#### ■ AI Software Stack

Boost the performance for RISC-V AI and IoT applications with optimized AndeSoft™ DSP, Vector and NN libraries

## **AndeSight™ IDE Free Download**

- Previous version for evaluation

- **■** Three-month time limit