Andes Technology USA Corp. Announces Major Expansion of Its U.S. Operation

- Post author:Lee Claire

- Post published:2021-10-08

- Post category:晶心新聞

Company Announces Job Openings for San Jose Headquarters and Portland R&D Office

San Jose, California October 8, 2021 – Andes Technology USA Corp., the headquarters of North America operations of Hsinchu, Taiwan-based Andes Technology Corporation, a leading supplier of high efficiency, low-power 32/64-bit RISC-V processor cores and founding premier member of RISC-V International, today announced a major expansion of Its U.S. operation. Andes Technology USA is greatly increasing engineering headcount in both the San Jose, California headquarters and its Portland, Oregon research and development facility. Andes Technology USA is seeking engineers in the U.S. and Canada to work remotely or in the Portland or San Jose offices. Openings are available for design engineers, verification engineers, and field application engineers.

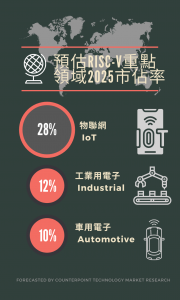

Andes Technology USA Corp. was established in 2015 as a California corporation coincident with Andes Technology Corp. joining RISC-V International. After Andes took the RISC-V instruction set architecture (ISA) as the base to form its fifth generation architecture, AndeStar™ V5 and started developing V5 processor IP’s, the U.S. operation was formed to be nearby early customer adopters of the new ISA. The U.S. subsidiary established an R&D lab shortly thereafter and began developing architectures for the high-end RISC-V processors. In under a year the investment together with the main engineering team in Taiwan yielded the first commercial RISC-V Vector processor IP which won nearly 10 projects including datacenter projects from a large OEM so far.

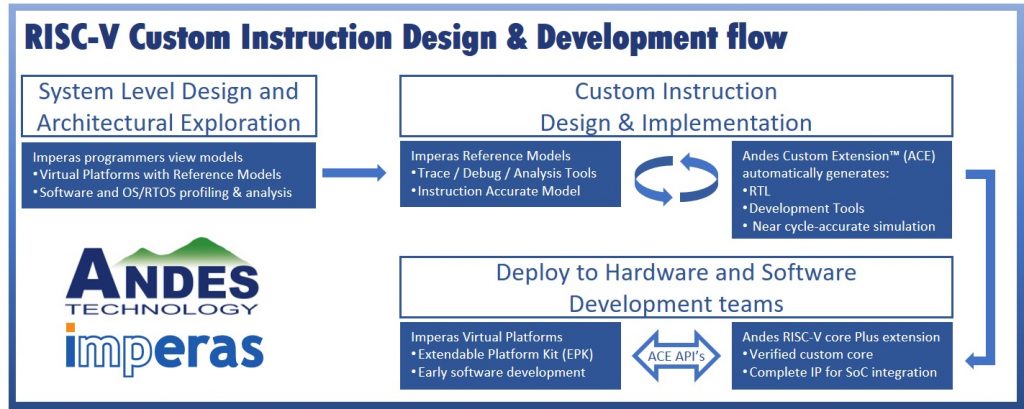

“Major semiconductor companies worldwide adopting the RISC-V ISA and the RISC-V International work groups rapid development of the RISC-V ISA extensions is driving demand for engineers to keep up with the fast pace of new technology development,” said Emerson Hsiao, Andes Technology USA Corp. Chief Operating Officer. “RISC-V customers like the growing number of extensions coming available as well as their ability to customize the architecture to better fit their processing requirements. Our tool Andes Custom Extensions (ACE) makes the customization process easier and less risky. To keep up with RISC-V technical developments and to serve our customers’ requests, we expect to greatly expand the size of our U.S. operation.”

Engineers interested in Andes are encouraged to view the open positions on the Andes Technology LinkedIn page.

About Andes Technology USA Corp.

Andes Technology USA Corp. was formed as a California corporation in 2015 in San Jose California to develop high-end CPU architectures. Emerson Hsiao, Chief Operating Officer heads the office, located in the heart of Silicon Valley in San Jose. In June 2018, the U.S. operation added its R&D facility in Portland, Oregon to attract engineers in the Pacific Northwest and Canada. To date, the U.S. operation continues to develop new high-end CPU processor architecture. Its most significant achievement is the development of the first RISC-V vector architecture based on the RISC-V International RVV specification. Andes developed the first RISC-V vector architecture based on version V0.8 of the specification and has advanced it to the latest to-be-ratified version.

About Andes Technology

Sixteen years in business and a Founding Premier member of RISC-V International, Andes is a leading supplier of high-performance/low-power 32/64-bit embedded processor IP solutions, and a main force to take RISC-V mainstream. Andes’ fifth-generation architecture AndeStar™ adopted the RISC-V as the base. Its V5 RISC-V CPU families range from tiny 32-bit cores to advanced 64-bit cores with DSP, FPU, Vector, Linux, superscalar, and/or multicore capabilities. The annual volume of Andes-Embedded SoCs has exceeded 2 billion since 2020 and continues to rise. To the end of 2020, the cumulative volume of Andes-Embedded™ SoCs has surpassed 7 billion.

About RISC-V AndesCore™

Andes Technology’s comprehensive CPU includes entry-level, mid-range, high-end, extensible and security families to address the full range of embedded electronics products, especially for connected, smart and green applications. From 2017, Andes expands its product line to RISC-V processors and provides a total solution in V5 family cores, including N22, N25F/NX25F, D25F, A25/AX25, A25MP/AX25MP, A27/AX27/NX27V, A45/D45/N45, AX45/DX45/NX45 and A45MP/AX45MP.

For more information, please visit https://www.andestech.com. Follow Andes on LinkedIn, Twitter, Facebook, and YouTube!

Contact Information

Andes Technology – hr@andestech.com