沈智明,資深經理,晶心科技股份有限公司

晶心科技所設計 IP 的目的,是滿足客戶實際需求,提供低成本高效率的產品給客戶,讓客戶可以做出極具競爭力的SoC,達到客戶與晶心科技雙贏的目的, 本文介紹的具 OSC 的 FreeRTOS 產品,巧妙的與 AndesCore™結合,客戶導入產品後,具競爭力與實用性,本文的目的期望能夠讓更多的讀者清楚這個產品的特性與優勢進而使用此產品。

某些電子產品的應用是不同的時間需要運行不同的功能,這時需要大空間的ROM 與 RAM 來存放與運行時會用到的各式各樣的功能。因為 CPU 同時間只會運行一種功能。所以在務實與經濟的考量下可以使用 overlay 的方式來滿足此類型產品的需求, 不但大幅降低 RAM 空間的使用,也達成硬體成本降低,使得產品競爭力大大的提升。達成 overlay 的方式有兩種,純軟體 overlay 與硬體加速 overlay。純軟體的 overlay 不須增加硬體,但軟體工程師寫程式時需自己配置functions 擺放的位置,容易出錯;呼叫 functions 時需要經過額外的處理,降低程式效能。因此純軟體的方法多用於只需偶而更換 overlay 的應用。例如 audio player,一條歌播完下一條開始前才需要檢查是否要用不同 decoder。我们有另一篇文章針對軟體 overlay 做介绍,本文不多加探討。

硬體加速的 overlay 使用少許硬體 gate count < 2K (OSC, Overlay SRAM Controller),提供軟體透明的 overlay 處理。軟體工程師寫程式時,可以假設有一個很大的連續程式空間,完全不需配置 functions 擺放的位置,這大大增加開發程式的效率;同時,呼叫 functions 時完全沒有任何純軟體方式的 overhead。上述之 OSC 優點可以符合客戶之需求,如果客戶系統複雜,要做的事比較多,需要用到多工(Multi-tasking),則晶心科技「支援 OSC 的 FreeRTOS 產品」就是最佳解方案。

1. Andes OSC 工作原理

先設定AndesCore™ NCEOSC100 IP中暫存器,再與運行軟體做整合搭配, 即可執行OSC的功能。

1.1 設定 OSC IP 的暫存器與動作解說

• OSC Control Register, OSCCTRL (+0x00)

• OVL_SZ: 3’h4 (16KB) RO/WI

• OVL_VALID: 0

• Fixed Region Size Register, OVLFS (+0x04)

• OVL_FSZ: 8’h18 (96KB) RW

• Overlay Region Base Register, OVLBASE (+0x08)

• Overlay Region End Register, OVLEND (+0x0C)

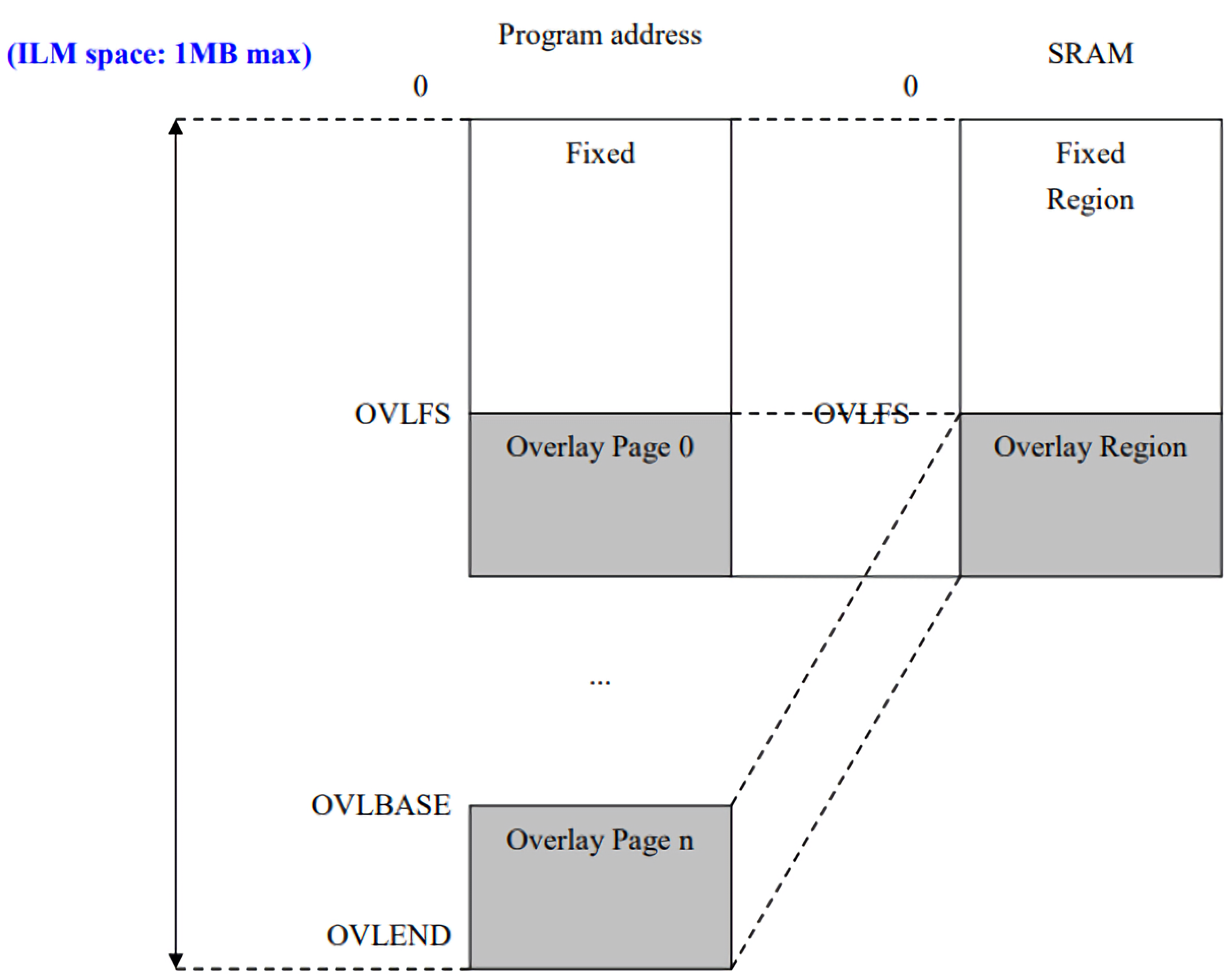

在OSC設計中SRAM分為兩個區域一個是”fixed region” 另一個是 “overlay region”,fixed region 為低位址的 SRAM ,其大小由OVLFS 暫存器設定。overlay region 是一個動態的區域,其位址由OVLBASE暫存器設定,大小由OVL_SZ 設定。當CPU運行時存取位址落在暫存器 OVLBASE與OVLEND之間時OSC將自動轉址到SRAM的overlay region內,如圖1所示。

因應實際需求設定多個Overlay 區域,當發生 ”Overlay Miss” 時,經由Overlay Exception的機制與軟體的搭配,可以將storage 中的 overlay page N 複製到 SRAM 中的Overlay Region,如圖1所示。關於overlay page 置換的工作原理將於下兩個章節中做說明。

圖 1. Overlay 範例說明

CPU運行時存取位址不在fixed region 或是當時有效的 overlay page 時,會發生Overlay Miss。當o Miss 發生時OSC會產生illegal instruction (32’hcoddcodd) 造成general exception。因為也有其他原因也會產生general exception,如何區分出overlay miss 與其他general exception於下個章節說明。

1.2 Overlay Exception 偵測

當進入 general exception 時可透過軟體檢驗下列程序來判斷是否為overlay

miss:

Step 1 如果 interrupt level 已經到達最大值 (PSW.INTL == Max INTL) ,這是 fetal error 不是overlay miss。

Step 2 必須是ITYPE.EYPE==1,才有機會是overlay miss。

Step 3 檢查IPC值,如果是落在fixed region 或是當時有效的 overlay page 時,這是真正的 illegal exception case. 如果不是在這兩個區域則是overlay miss。

經過前面3步驟驗證,如果確定是overlay miss,則可進行Overlay exception handling 的動作。

1.3 執行 Overlay Exception Handling 的動作

確定 overlay miss 後,做更新overlay region的動作。

Step 1 得到新的overlay region 位址:

– 從IPC得到更新overlay page的起始位置。

– 更新OVLBASE 暫存器。

Step 2 更新的overlay page內容複製到 SRAM 中的overlay region

Step 3 最後執行iret返回overlay miss發生時的位址。

2. 具 OSC 的 FreeRTOS 介紹

Andes 結合OSC 與 FreeRTOS設計出具 OSC的FreeRTOS ,OSC的功能與原理已經介紹於上個章節,本章節將說明具 OSC的FreeRTOS與一般的FreeRTOS 的差異處,並列舉範例程式的運行展現OSC與FreeRTOS的功能。

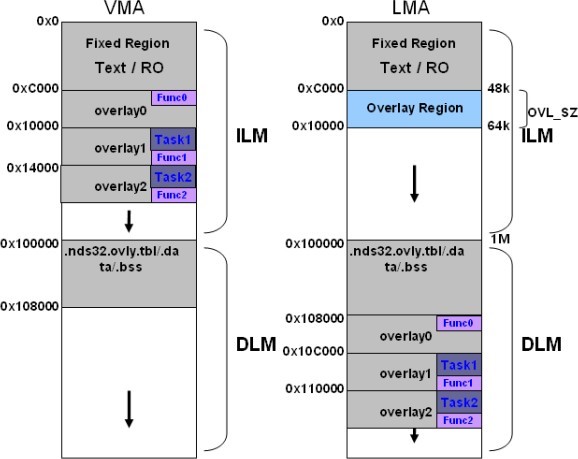

2.1 具OSC的FreeRTOS記憶體配置

具OSC的FreeRTOS的記憶體配置如圖2 , 範例程式的linker script設定了LMA(系統image)的記憶體配置模式,其中overlay0, overlay1 與 overlay2是模擬storage 的位址。linker script 設定VMA(系統執行時)的記憶體配置模式,當系統運行進入overlay1,2.. 時產生overlay miss 觸發 exception 將overlayN 內的資料複製到 overlay region 中,這樣的設計達到一份Overlay Region 的SRAM空間可以在不同時間執行對應不同的overlayN程式碼的目的。

圖 2.具 OSC 的 FreeRTOS 記憶體配置圖

2.2 osc_hisr task

從圖2的overlay0,1,2 中可以發現系統會運行task1與task2。說明FreeRTOS 做overlay region置換時也會執行scheduler 做置換task 的工作。本範例程式設計是在standard FreeRTOS 中增加一個 osc_hisr task 做overlay region 置換與管理的工作。如何達到OSC 與 osc_hisr task的結合需從Overlay Exception Handling的動作開始研討:

• 當 overlay exception 被觸發時,送 message 給 queue 啟動 osc_hisr task。

• 因為 osc_hisr task 做 overlay region 資料的置換,所以 osc_hisr task 尚未執行完成前,不可以執行 Overlay Exception Handling 的 iret.

osc_hisr task 的主要工作在:

• Map overlay region

• overlay region 資料的複製

osc_hisr task 設計的原則:

• 此 task 必須是最高 priority task.

• 此 task 必須放在 fixed region.

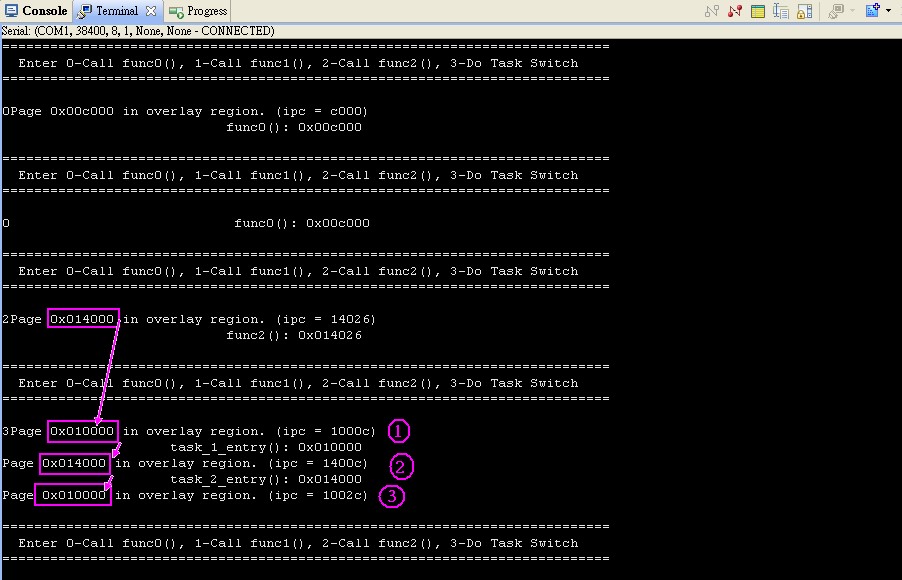

2.3 範例程式運行

具 OSC 的 FreeRTOS 在 Andes EVB 上直接運行得到的結果如圖 3,範例程式中鍵入 3 時,是進行 task 轉換,因為不同 task 運行相對應的 overlay function 從console task 轉成task1 再轉成task2 也會產生相對應的page fault 執行osc_hisr task。圖 3 紅色箭頭與數字轉變可以得知 task 轉換啟動 function overlay 運作,從此範例程式中可同時驗證 OSC 與 FreeRTOS 兩者的功能。

圖 3.範例程式執行結果

3. 結語

本文第一章說明 Andes OSC 的工作原理與功能,第二章說明 FreeRTOS 如何與 Andes OSC 整合運作,在 OSC 的 FreeROTS 中也增加一個最高 priority task “osc_hisr” 來執行 OSC 相對應的功能,進而說明了具 OSC 的 FreeRTOS 需注意的設計原則,具 OSC 之 FreeRTOS 是由軟體與硬體單元所組成,兼具硬體的效能與軟體的彈性。

已經有業界客戶取得 Andes 的具 OSC 之 FreeRTOS 開發出具競爭力產品在市面上銷售,由此可知具 OSC 之 FreeRTOS 具有經濟實用的價值,可以協助客戶在使用 AndesCore™時,設計出具有彈性且高附加價值之產品。