王勝雯,經理,晶心科技股份有限公司

在現今 SOC 設計中,當周邊裝置(Periphral IP)想要和中央處理器(CPU)溝通時,最常使用的機制則是透過中斷(Interrupt)。由周邊裝置觸發中斷給中央處理器,當中央處理器接收到中斷後,則可判斷是由哪個周邊裝置觸發些中斷,接著處理相對應的中斷處理程式(ISR,Interrupt Service Routine),藉此達到彼此溝通的目的。但在同時間若有多個周邊裝置同時觸發中斷給中央處理器時,優先處理程序就成為了非常重要的一環。

Andes Core™在中斷優先權處理方面,共支援兩種模式:固定中斷優先權(Fixed Priority)和可程式化中斷優先權(Programmable Priority)。當配置在固定中斷優先權時,中斷處理優先權會依照中斷輸入腳位的順序來決定優先處理權,腳位數字越小其優先權越高(Low Interrupt Input Number High Priority),而配置在可程式化中斷優先權時,可將所有中斷輸入設置成四個層級的優先處理權,中央處理器在同時發生觸發中斷時會依照其設置的層級來決定優先處理權,若發生層級相同時則再以中斷輸入腳位的順序來決定優先處理權。

而在中央處理器進入中斷處理程序後,倘若希望能讓其他優先權較高的中斷觸發中央處理器進而處理該中斷處理程序,在軟體部分又應該怎麼設置來達到巢狀中斷的結構,我們將在本文介紹給使用者參考,期望能對使用者有所助益,也希望讀者不吝指教提供您寶貴的意見。

1. 中斷優先權介紹

AndesCore™共支援兩種中斷優先權處理模式:固定優先權模式(Fixed Priority)與可程式化優先權模式(Programmable Priority)。以下的介紹將架構於AndesCore™ N801-S 這顆中央處理器。帶領使用者循序漸進地,了解這兩種中斷優先權處理模式的差異。

1.1. Definition

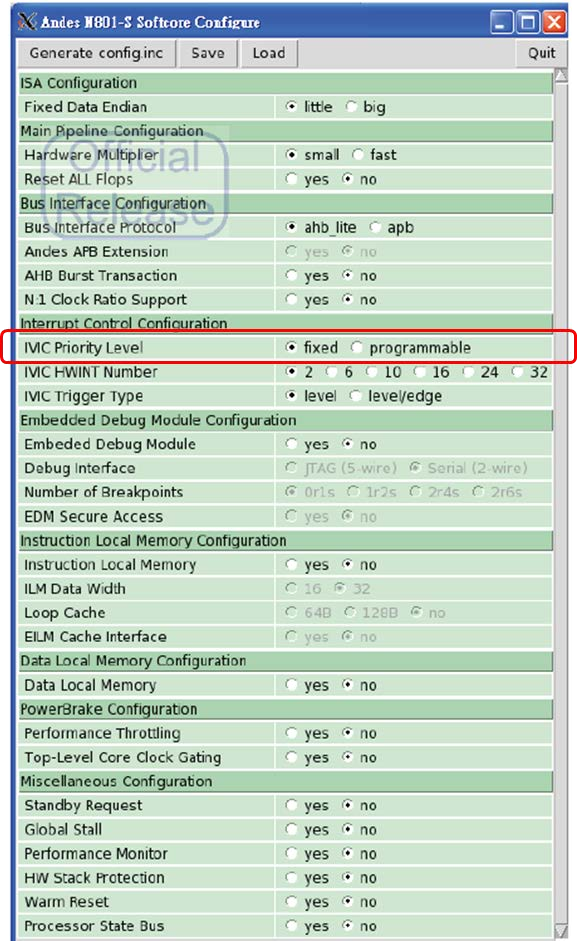

AndesCore™ N801-S支援兩種中斷優先權模式,在硬體配置時就需要先決定中斷優先權的模式,如圖1的硬體配置視窗所示,首先,我們先介紹關於這兩種模式的定義。

圖1. 硬體配置視窗

1.1.1 Fixed Priority Mode

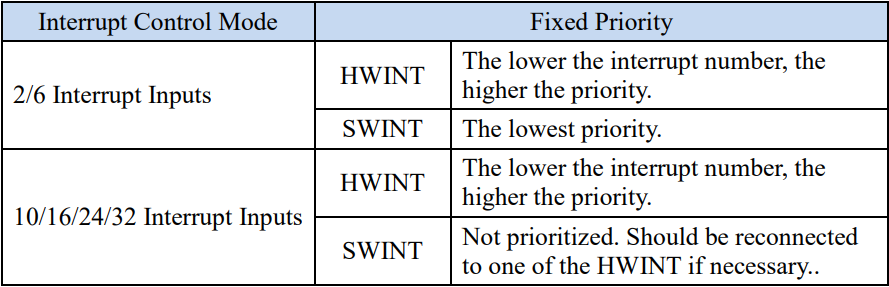

在AndesCore™ N801-S硬體配置時,若配置在中斷固定優先權模式下,中央處理器在多個觸發中斷同時發生時,則依照中斷輸入腳位來決定處理順序,請參考表1。

表1. Fixed Priority Mode 觸發中斷處理優先順序

1.1.2 Programmable Priority Mode

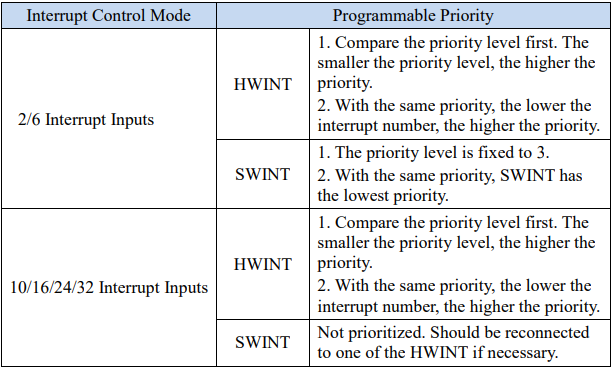

在AndesCore™ N801-S硬體配置時,若配置在中斷可程式化優先權模式下, 中央處理器在多個觸發中斷同時發生時,則依照每個中斷輸入設置的優先層級來決定處理順序,請參考表2。而在可程式化優先權模式下,每個中斷輸入都有四個優先層級可以讓使用者自行設置,使用者也可以透過系統暫存器(PPL2FIX_EN) 將模式從可程式化優先權模式切換至固定優先權模式。

表2. Fixed Priority Mode 觸發中斷處理優先順序

1.2. System Register

關於上述兩種中斷優先權模式,在可程式化優先權模式下使用者可透過設置AndesCore™ N801-S 內部的 system register 來設置每個中斷優先權層級,以及將可程式化優先權模式切換回固定優先權模式。

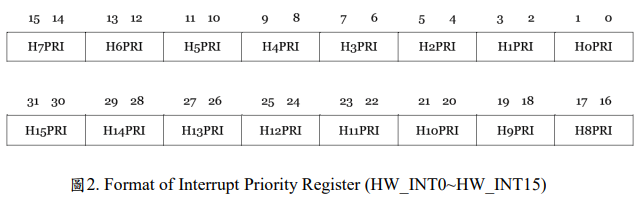

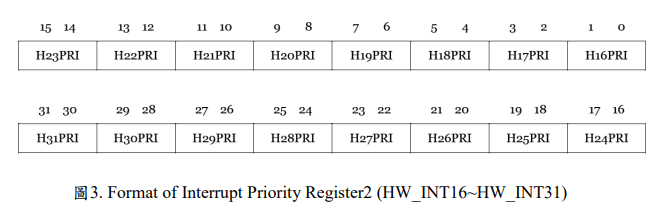

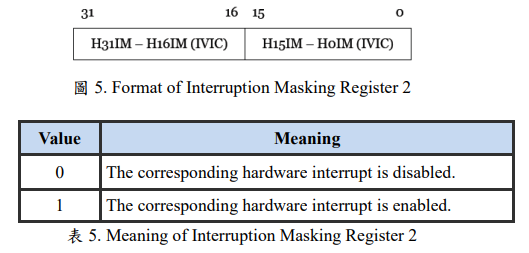

設置優先權的system register為INT_PRI(ir18)與INT_PRI2(ir28),每個中斷輸入都有四個層級讓使用者規劃,其格式如圖2與圖3的暫存器配置,而設定值的優先權可參考表3的解釋。

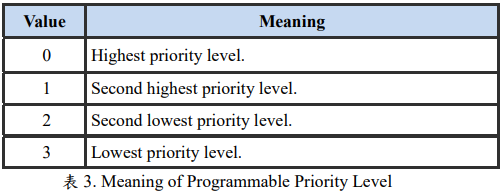

在硬體配置成可程式化優先權模式下時,有一個system register 為INT_CTRL(ir19)。透過設置INT_CTRL.0,使用者在硬體配置成可程式換優先權模式下切換回固定優先權模式。其格式如圖4的暫存器配置,而內容值的意義可參考表4的解釋。當PPL2FIX_EN=1時,CPU處理中斷的方式則會與硬體配置成固定優先權模式的情況一樣,CPU只根據中斷輸入的號碼大小來決定處理順序。

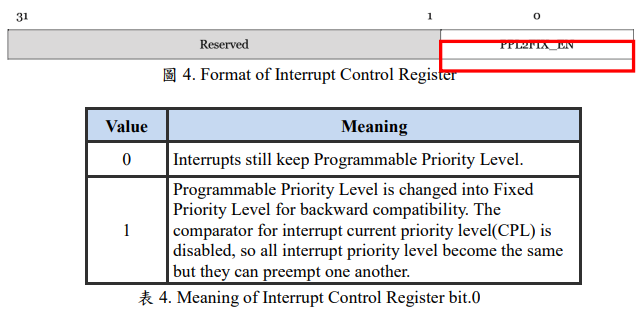

另一個控制中斷輸入 on/off 的 system register 為 INT_MASK2(ir26),使用者可以透過設定該暫存器來決定各中斷輸入是否開啟。

2. 中斷優先權處理程序介紹

在介紹完中斷處理模式相關定義之後,本章節提供在實際整合與應用上的

範例,讓使用者可更了解在不同中斷處理模式下的差異。

2.1. Multi-Interrupt at Fixed Priority Mode

本章節介紹當硬體配置在固定中斷優先權模式下時,發生多個中斷時,CPU 在處理的程序。

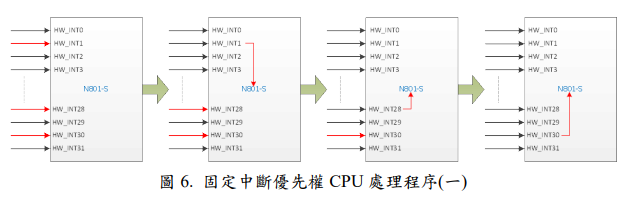

圖 6 中,表示同時發生 HW_INT1、HW_INT28 與 HW_INT30 三個中斷源, 此時CPU 會依照中斷輸入號碼大小(號碼越小優先權越高)來決定處理優先順序, 所以 CPU 依序先處理 HW_INT1,然後再接著處理 HW_INT28,最後再處理HW_INT30。

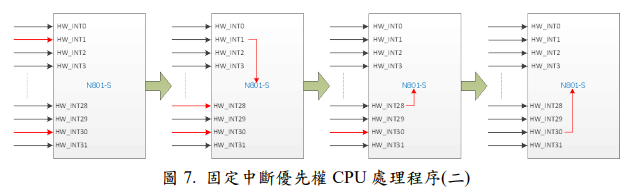

圖 7 中,表示同時發生 HW_INT1 與 HW_INT30 兩個中斷源,在 CPU 處理完 HW_INT1 後應該接著處理 HW_INT30,但在處理 HW_INT1 的同時,外部中斷源又接著發生 HW_INT28,所以在 CPU 在處理完 HW_INT1 後會優先處理HW_INT28,然後最後才處理 HW_INT30。

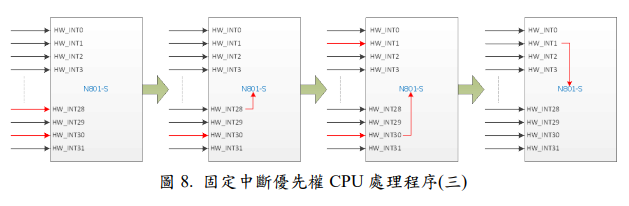

圖 8 中,表示同時發生 HW_INT28 與 HW_INT30 兩個中斷源,在 CPU 處理完 HW_INT28 後接著處理 HW_INT30,此時外部發生了 HW_INT1,在沒有使用巢狀中斷的情況下,此時 CPU 已經在處理 HW_INT30,所以並不會因為HW_INT1 的中斷優先權大於 HW_INT30 而去處理 HW_INT1 ,必須等到HW_INT30 處理完畢,最後才處理 HW_INT1。

2.2. Multi-Interrupt at Programmable Priority Mode

本章節介紹當硬體配置在可程式化中斷優先權模式下時,發生多個中斷時,CPU 在處理的程序。

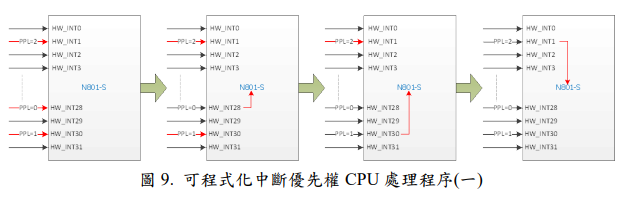

圖 9 中 , 表 示 同 時 發 生 HW_INT1(PPL=2) 、 HW_INT28(PPL=0) 與HW_INT30(PPL=1)三個中斷源,此時 CPU 會依照中斷優先權大小(PPL 值越小優先權越高)來決定處理優先順序,所以 CPU 依序先處理 HW_INT28(PPL=0),然後再接著處理 HW_INT30(PPL=1),最後再處理 HW_INT1(PPL=2)。

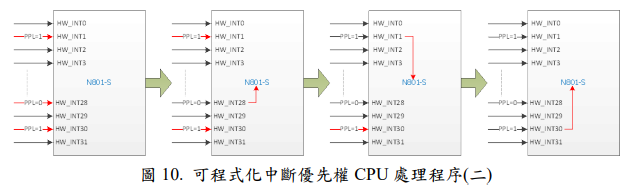

圖 10 中, 表示同時發生 HW_INT1(PPL=1) 、 HW_INT28(PPL=0) 與HW_INT30(PPL=1)三個中斷源,此時 CPU 會依照中斷優先權大小來決定處理優先順序,而發生中斷優先權大小相同時,則再依照中斷號碼大小(號碼越小優先權越高) 來決定處理優先順序。CPU 依序先處理 HW_INT28(PPL=0),此時HW_INT1(PPL=1)與 HW_INT30(PPL=1)的 PPL 相同,CPU 則依照中斷輸入號碼大小來決定優先順序,所以先接著處理 HW_INT1(PPL=1) ,最後再處理HW_INT30(PPL=1)。

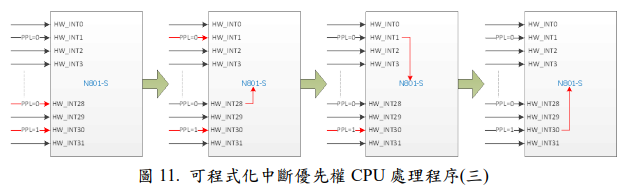

圖 11 中,表示同時發生 HW_INT28(PPL=0)與 HW_INT30(PPL=1)兩個中斷源,此時 CPU 會依照中斷優先權大小來決定處理優先順序,所以 CPU 先處理HW_INT28(PPL=0),但在處理 HW_INT28(PPL=0)的同時,外部中斷源又接著發生 HW_INT1(PPL=0),所以 CPU 在處理完 HW_INT28(PPL=0)後會優先處理HW_INT1(PPL=0),最後再處理 HW_INT30(PPL=1)。

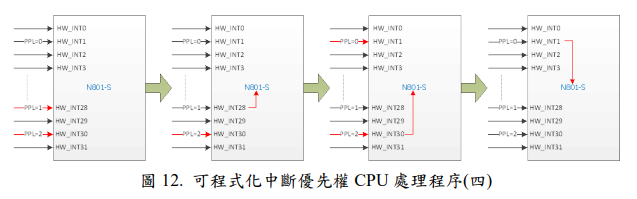

圖 12 中,表示同時發生 HW_INT28(PPL=1)與 HW_INT30(PPL=2)兩個中斷源,此時 CPU 會依照中斷優先權大小來決定處理優先順序,所以 CPU 先處理HW_INT28(PPL=1) , 然 後 接 著 處 理 HW_INT30(PPL=2) , 但 在 處 理HW_INT30(PPL=2)的同時,外部中斷源又接著發生 HW_INT1(PPL=0),在沒有使用巢狀中斷的情況下,此時 CPU 已經在處理 HW_INT30(PPL=2),所以 CPU 並不會因為 HW_INT1(PPL=0) 的優先權大於 HW_INT30(PPL=2) 而去處理HW_INT1(PPL=0) , 必須等到 HW_INT30(PPL=2) 處理完畢, 最後才處理HW_INT1(PPL=0)。

3. 結語

透過上述的幾種多個中斷源發生時,N801-S 在處理程序上的方式,相信各位對於固定與可程式化中斷優先權的使用有了更進一步的了解,對於在中斷源的配置上就能依照電路需要來規劃輸入腳位以及靈活運用可程式化優先權中斷的功能。

在 AndesCore™所提供的兩種中斷優先權模式裡,CPU 在進入中斷處理程序後,硬體會自動將 GIE(Global Interrupt Enable)關閉,讓 CPU 能專注於處理當前的中斷程序,然後在處理完畢中斷程序後硬體再自動將 GIE 開啟,但是如果使用者希望能夠在中斷處理程序過程中又允許優先權更高的中斷源能夠介入,並且讓 CPU 能夠暫停當前的程序,進而優先處理該更高優先權的中斷,AndesCore™ 也支援這樣的巢狀中斷(Nested Interrupt)處理模式,而那又是另一個課題了,我們將在之後的技術文章中再針對AndesCore™巢狀中斷的程式處理方式有更詳細的應用方式與介紹。