RISC-V CON開講!日期:2022/8/4 (四)

時間:13:25-17:10

近年RISC-V以開源、精簡及可擴充的彈性配置備受矚目,在全球掀起運算新風潮。32/64位元嵌入式CPU核心供應商晶心科技身為RISC-V協會創始首席會員,已推出多款RISC-V處理器解決方案。為了進一步推廣RISC-V,晶心將於8月4日在新竹國賓飯店舉辦年度RISC-V CON研討會,今年首度採實體暨線上並行方式,以「引領RISC-V運算大時代‧駕馭未來多元新應用」為主題,介紹改變新興運算面貌的RISC-V靈活優勢,並分享晶心協助RISC-V生態系實現多元應用的創新技術。為了迎接從終端到雲端的新興運算時代,全球科技大廠紛紛擁抱RISC-V。RISC-V國際協會(RISC-V International)的企業會員已超過300家,快速壯大的生態陣容,顯示出適合人工智慧、物聯網、伺服器、資料中心等多元應用的RISC-V架構逐漸成為業界主流。晶心布局RISC-V多年,致力於發展以RISC-V架構為基礎的創新處理器核心及開發平台,並推出一系列高效能且低功耗的RISC-V處理器核心,包含DSP、FPU、Vector、超純量(Superscalar)及多核心系列,同時與諸多合作夥伴通力合作,攜手打造完善的RISC-V生態系及產業鏈。

本次RISC-V CON開場將由晶心科技董事長暨RISC-V國際協會董事林志明以「RISC-V蔚為運算主流」為題,放眼國際,分析RISC-V成為業界主流標準的原因、規格批准(ratification)的趨勢及影響的應用領域。晶心科技總經理暨技術長蘇泓萌則將主持研討會最後的Q&A,進一步解說關於RISC-V的最新技術發展動態。

除此之外,RISC-V CON將剖析全方位的RISC-V高效運算解決方案,適合資料中心、高效能運算(HPC)以及AI Cloud端等級應用開發,同時探討RISC-V如何實現車用晶片對於資訊安全、功能安全與可靠度的技術要求,另解析發展快速的AIoT與TinyML應用,介紹契合AI運算需求並兼具性能和效率的RISC-V解決方案。

此外,本次研討會還邀請到眾多RISC-V生態夥伴進行專題演講及現場展示,其中MCU龍頭瑞薩電子將分享採用RISC-V的微處理器解決方案,eFPGA領導廠商Menta則將介紹如何結合RISC-V讓客戶自定指令(ACE)在eFPGA中更容易重新編置,為開發和差異化保留發展空間。其他參展商還包括編譯器軟體大廠IAR Systems、物聯網量子驅動網路安全專家Crypto Quantique等等,將一同帶來最新RISC-V應用與技術趨勢。

本次研討會將採實體與線上並行,報名並參加實體場次者可參與抽獎,現場還有豐富贈品讓你帶回家!(名額有限,額滿為止)

◎ 本研討會直播結束後,不另提供重播觀看。

活動議程

報到

Opening

RISC-V Everywhere: The Momentum and Future of RISC-V Growth Globally and across Industries

Calista Redmond, CEO, RISC-V International

RISC-V 蔚為運算主流

RISC-V Evolves into Mainstream of Computing

林志明, 董事長暨執行長 晶心科技

In this presentation, why and when RISC-V is in industrial mainstream will be analyzed. The trend of RISC-V instruction sets ratification will be introduced, which will help audience to know more about RISC-V’s powerful features and strength. Also, a few emerging applications which RISC-V are strong with will be introduced too.

解密RISC-V : 高效運算的RISC-V全方位解決方案

Demystifying RISC-V : Comprehensive RISC-V Solutions for High Performance Computing

王勝雯, 客製運算部 技術服務處 處長 晶心科技

RISC-V 架構指令模組化的優勢讓使用者可以自行定義CPU的架構,進而完成「高算力性能CPU」這個課題,

本次演講將從RISC-V 指令分群概念開始,以及說明 Andes 設計團隊是如何發展出一套自定義擴展指令架構的工具。

並介紹Andes 低功耗高效能的25/27系列,到超高算力的45MP系列,如何應用到Data Center、HPC以及AI Cloud端等級CPU開發。

深入瞭解車用晶片技術要求並探討如何與RISC-V完美結合

The Requirements of Automotive Chips and How It Greatly Fits with RISC-V Cores

洪彰辰, 業務發展處 副處長 晶心科技

近五年汽車電子電氣架構因為內外部因素,有許多重大的演進,同時供應鏈的晶片短缺,

新能源車的興起,軟體定義汽車的潮流,造就一股汽車新勢力,除了車廠比以往更願意敞開大門接受最新技術,

更多晶片公司與軟體公司也紛紛加入汽車供應鏈。RISC-V做為前三大CPU指令集架構之一,

除了效能,面積和功耗等關鍵特色具有競爭優勢,在資訊安全、功能安全跟可靠度上面,都能與生態夥伴一起提供符合法規的解決方案。

Renesas Pioneers RISC-V Technology on RZ/Five General-Purpose MPUs With SLTS CIP Linux Solution

Mamoru Nomura, Sr. Director of MPU Business Development, Renesas

茶歇:RISC-V解決方案展示

Reconfigurable ISA Extension Using eFPGA as a Co-extended Reconfigurable Core Tightly Coupled within Andes RISC-V Core

Imen Baili, Product Marketing Lead, Menta

Andes is working with Menta to enable embedded programmable logic through eFPGA in its RISC-V AndesCore™ families.

Menta and Andes share the same vision, providing customers with a joint solution that allows instruction set architecture (ISA) extension to be added or changed in the field.

Extending RISC-V ISA with custom instruction set extension, based on eFPGA co-extended core, is the key differentiator for the next processor unit’s generation.

Designers will be able to add any instruction they need for the function that they want to accelerate, in the field.

This is a powerful feature that does not break any software compatibility and leaves space for development and differentiation.

The eFPGA plays the role of a hardware co-extended core for the RISC-V CPU,

unlocking the possibility to add or reconfigure ISA for the duration of the product’s life.

Andes RISC-V processor families, already available in the SoC market as a mainstream computing engine,

are now looking to enhance the product’s ACE (Andes Custom Extension™) feature by extending it with eFPGA hardware support.

使用 Imperas 和 Andes ACE 進行軟件驅動的設計優化

Software driven design optimizations with Imperas and Andes ACE

Katherine (Kat) Hsu,Senior Account Manager,Imperas Software

本演講將概述使用 Imperas 參考模型和分析工具為您的應用程序優化 Andes ACE 擴展的架構探索過程。

This talk will outline the architectural exploration process to optimize Andes ACE extensions for your applications using the Imperas reference models and analysis tools.

This talk will outline the architectural exploration process to optimize Andes ACE extensions for your applications using the Imperas reference models and analysis tools.

IAR Systems - 不斷推陳出新,讓RISC-V開發變得更容易

蔡本中,資深應用工程師 IAR Systems

IAR Systems於2019年開始針對RISC-V架構,推出整合開發工具EWRISC-V,之後陸續推出了功能安全版本、支援64bit高階應用、支援更多第三方軟體。除此之外,近年來更是加入VS-Code支援、多核心除錯以及Linux開發工具。

本次會議將進一步介紹這些IAR Systems如何讓RISC-V體系更完整以及讓RISC-V使用者開發變得更容易。最後也會分享一些大中華區SoC廠商使用IAR的案例。

解析AIoT與TinyML需求 契合RISC-V 計算效率與彈性

Accelerating AIoT and TinyML Computation with Andes RISC-V Processors

王庭昭, 技術經理 晶心科技

TinyML被視為現代快速發展的AI技術領域,從硬體、演算法到軟體的高度協作,以極低的功耗與極高的效率運行,

實現各種長時間Always-on的應用,將智慧物聯網(AIoT) 應用更進一步深化。與此同時遇上新世代的RISC-V處理器指令技術,

與生俱來的低功耗、高效率、彈性以及擴充性正符合TinyML所必須。

在本次演講中,我們將展示 RISC-V 簡潔與模組化的設計,如何使得晶片的面積更小與更低的功耗。 探討RISC-V DSP/SIMD P-extension 擴展指令集顯著加速於智慧語音、圖像和影像的計算效能, 與RISC-V Vector V-extension擴展指令集展開於數據密集型計算。再進一步演示對於追求終極性能效率的需求, RISC-V 的自定義擴展指令創造的全新空間。最終融合所有優勢並緊密結合軟體SDK,產出一個性能與效率兼具, 具備差異化又貼近TinyML應用的處理器解決方案。

在本次演講中,我們將展示 RISC-V 簡潔與模組化的設計,如何使得晶片的面積更小與更低的功耗。 探討RISC-V DSP/SIMD P-extension 擴展指令集顯著加速於智慧語音、圖像和影像的計算效能, 與RISC-V Vector V-extension擴展指令集展開於數據密集型計算。再進一步演示對於追求終極性能效率的需求, RISC-V 的自定義擴展指令創造的全新空間。最終融合所有優勢並緊密結合軟體SDK,產出一個性能與效率兼具, 具備差異化又貼近TinyML應用的處理器解決方案。

Q&A及好禮抽獎

林志明, 董事長暨執行長 晶心科技

蘇泓萌, 總經理暨技術長 晶心科技

講者陣容

林志明

晶心科技 執行長

蘇泓萌

晶心科技 總經理暨技術長

王勝雯

晶心科技 客製運算部 技術服務處 處長

王庭昭

晶心科技 技術經理

洪彰辰

晶心科技 業務發展處 副處長

Mamoru Nomura,

Sr. Director of MPU Business Development, Renesas

Imen Baili,

Product Application Engineer, Menta

蔡本中,

IAR SYSTEMS資深應用工程師

Katherine (Kat) Hsu

Senior Account Manager, Imperas Software Ltd

活動好禮

報名並全程參加者即有機會抽中幸運好禮!

OPPO手機一隻

頭獎1名

JBL 電競無線耳機一台

二獎1名

小米 Router一台

三獎1名

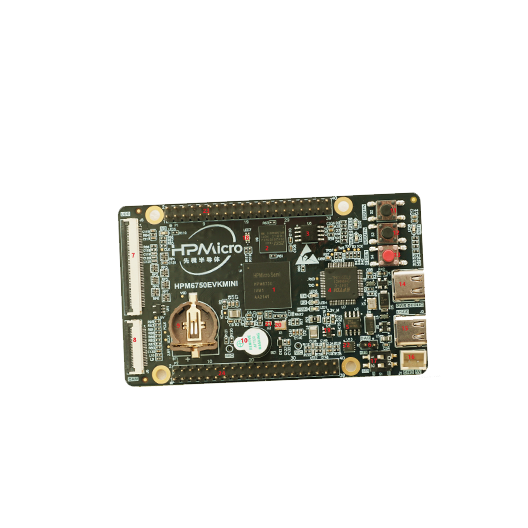

HPMicro Test Board 6750

特別獎

伸縮支架三合一充電線

問卷禮

品牌環保袋

問答禮/早鳥禮

品牌口罩

參加禮

參加辦法

- 本研討會採預先線上報名,請勿偽造他人身份資料進行報名以免觸犯法律。

- 主辦單位保留報名資格之最後審核,將以主題及屬性符合者為優先考量。為加速審核,敬請使用公司電子信箱報名。

- 通過審核者,系統將以電子郵件方式寄發「報到通知」或「收視連結」至您的電子信箱

- 本研討會直播結束後,不另提供重播觀看。

- 凡參加本次活動所舉辦之抽獎,因有登錄資料不實或冒用他人身份等,主辦單位有權取消其得獎資格。

- 主辦單位保留修改本活動內容和規則之權利,毋須另行作出解釋或通知。